基于FPGA的星载计算机自检EDAC电路设计

在本设计中,我们采用外置的CPU芯片和内置的RAM单元,作为自检EDAC电路的硬件平台 (或环境、资源)。CPU芯片在这里起到的作用是启动EDAC自检,处理错误中断,向地面传 送错误信息,并根据地面要求对错误信息进行处理。

在该设计中,检测一个存储单元地址仅需要4个时钟周期,如果开启自纠错功能,并且 检测到单比特错误,再增加2个时钟周期用来纠错。因此如果时钟为20MHz,并且错误数据较 少,则更新1M个RAM存储单元需要的时间约为:4×1M 20MHz = 0.2s。

更重要的是,在这0.2s的时间里,仅在出现错误时需要向计算机产生中断,进行相应处 理,对地面进行错误报告,因而CPU处理时间很短,节省了宝贵的CPU资源。

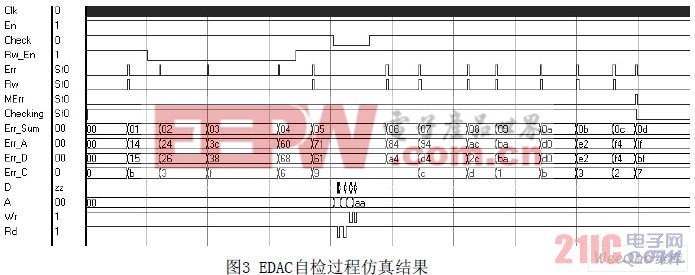

3.3 仿真与验证

在空间环境下普遍存在的SEU,在地面环境下是很难获得的,为了在地面对该EDAC电路 设计进行验证,需要采取故障注入手段。由于在本例中RAM存储单元采用FPGA内部资源,因 此故障注入变得相对简单。在FPGA进行程序综合时,可将预先编制好的RAM存储单元初始化 文件一起综合。因此我们可在编制RAM存储单元初始化文件时,对某些比特位进行修改,以 模拟空间环境下SEU对RAM存储单元的影响。

在这里采用Xilinx公司的XQRV300为硬件载体,该型号FPGA芯片在航天领域内被广泛使 用。为节省仿真时间,数据RAM存储单元采用256*8bit,检验RAM存储单元采用25*bit。在 RAM存储单元初始化文件中,人工加入了12个单比特错误,以及1个两比特错误,如下表所示。

为仿真简便起见,向存储单元存放的正确数据与存储单元地址相同。

时钟选择为20MHz,通过采用ModelSim软件进行布线后仿真,我们可以得到图3所示结果。

图中: Clk — 系统时钟;

En — EDAC 模块使能控制;

Check — 自检启动/使能信号(信号上升沿触发一次巡检,信号为低暂停巡检);

Rw_En — 自纠错使能信号(为高允许纠错);

Err — 错误中断(标志)信号;

Rw — 自纠错标志信号(为高表示正在进行自纠错操作);

MErr — 多比特错误中断(标志)信号;

Checking — 自检标志(为高表示尚未完成本次巡检操作);

Err_Sum,Err_A,Err_D,Err_C — 错误计数,错误地址,原始数据,原始校验码;

D,A,Wr,Rd — 单片机数据、地址、写操作、读操作信号;

评论