基于FPGA的星载计算机自检EDAC电路设计

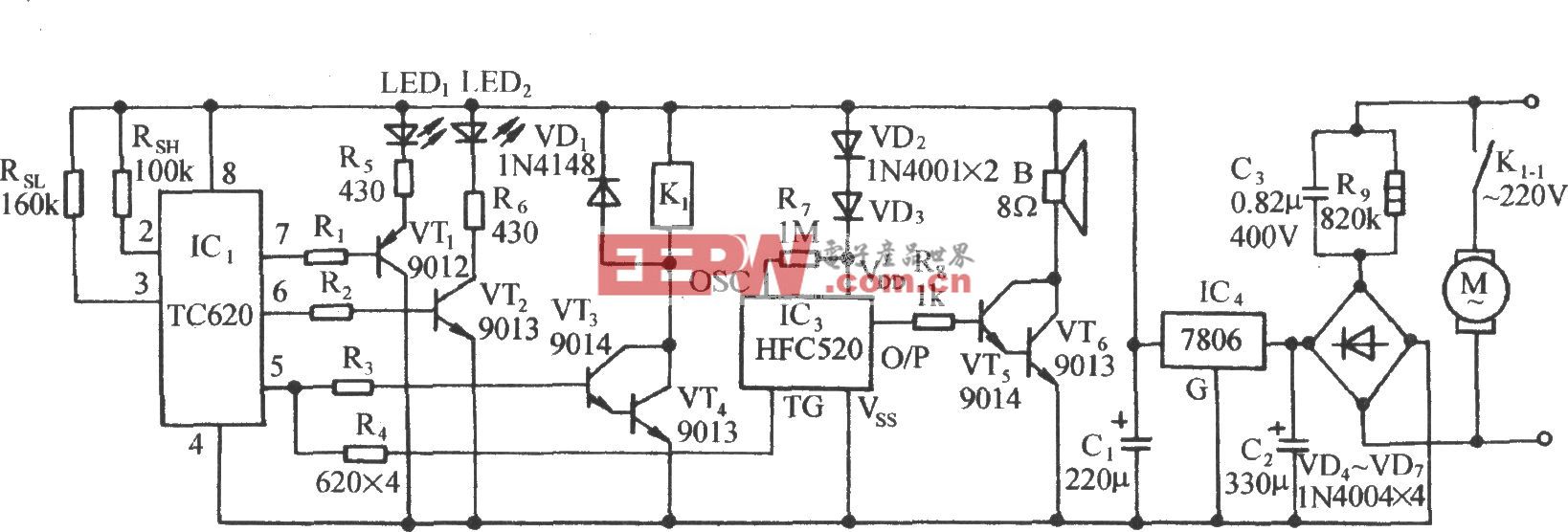

从图中可以看出,启动EDAC自检后,EDAC开始巡检RAM存储单元,产生错误中断(标志) 信号,给出错误信息。当单片机需要处理中断时,将Check信号置‘0’,可暂时停止巡检, 此时单片机可对RAM存储单元进行正常读写操作。等中断处理完后,单片机将Check信号置 ‘1’,恢复RAM巡检操作。

另外可通过Rw_En的置‘0’或‘1’,来控制禁止或允许进行自纠错操作。

当出现可识别的多位错误时,产生Err和MErr两个错误中断(标志)信号,但由于汉明码仅能纠正单比特错误,因此不进行自纠错操作。

从原注入错误数据对应的地址读出数据,仿真输出结果如图4所示。

可以看出除最后一个地址(FFH)由于两位错仍输出错误外,其他地址输出数据均与地址相同,即为正确数据。

其中,24H、3CH、60H三个地址虽然输出正确数据,但仍报错,表明存储器内数据仍然 为错误数据,在输出时进行了纠错。这是由于在上次巡检到这部分地址空间时,通过把Rw_En 信号拉低,从而禁止了自动纠错,导致这三个地址错误数据未被纠正。而在对其他地址进行 数据读取时,未产生错误标志,证明其他错误数据已被纠错。

4 结论

本文在采用FPGA芯片实现基本EDAC读写功能的设计思路基础上,创建了一种新型的可对 RAM存储单元进行自检的EDAC功能模块。该模块不但可以对RAM存储单元进行快速巡检,巡检 时间仅为传统EDAC方法的十二分之一,还可以自动纠正已发现的错误。该模块最大的优点在 于节省了单片机资源,几乎不需要单片机的参与即可完成所有自检功能,从而使基于FPGA 的星载计算机对SEU事件防护能力得到较大的提升。本文中该模块采用Verilog硬件描述语言 编程,具有可移植性,这种设计方法可用于各种体系结构的星载计算机中。

本文作者创新点: 通过引入FPGA技术,设计了一种灵活、高效的自检EDAC电路,可在CPU 的控制下实现对错误信息的自动处理,并提出了该EDAC电路验证方法。

评论