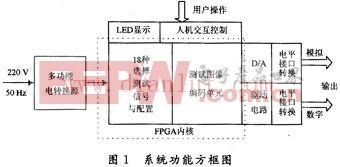

基于FPGA的数字电视CAS系统设计

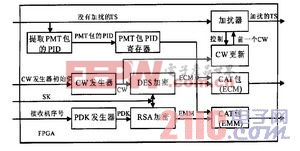

CAS发送端FPGA实现的框图见图2所示。接收机序号,SK(业务密钥)和CW(控制字)发生器的初始值由PC机通过单片机来对FPGA芯片进行设定。FPGA芯片先检测TS流中PMT包的PID值,将这个值与EMM、ECM一起形成CAT包,等待前端的复用器将其插入TS流中。加扰器会每隔几秒钟就对CW进行更新,用新的CW来对TS加扰,同时CW发生器又将产生下一个CW,经过密钥SK对CW进行DES加密后,形成新的ECM。再打包形成CAT,等待前端插入(复用)TS流中。EMM信息的形成与此类似。

图2

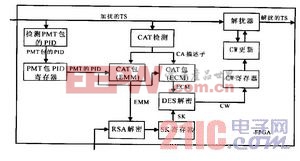

CAS接收端FPGA的实现

CAS接收端FPGA实现的框图如图3所示。PDK信息通过智能卡送给FPGA芯片。FPGA芯片先检测解复用之后的TS流中PMT包的PID值,将其存在寄存器里,然后继续寻找CAT表,再找到TS中的CAT时,将其中的CA描述子提取出来,再根据描述子中CA-system-ID的值来决定是提取ECM信息还是EMM信息,根据PDK和EMM可以解密出SK,再通过和ECM信息解密出CW。具体是使用当前的CW还是使用下一个CW来解扰,由解扰器根据TS包头信息来决定。

图3

结束语

本文介绍了数字电视条件接收的基本原理,并提出了一种只用CAT表来传送EMM、ECM信息的方法。该方法不但可以对单节目流进行加扰,还能支持多节目流加扰后的复用传输。而且相比用CAT、PMT分别传输EMM和ECM的方法,该电路更加简单,用FPGA也更容易实现。

评论