基于FPGA的帧同步提取方法的研究

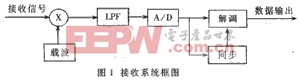

在可靠的通信系统中,要保证接收端能正确解调出信息,必须要有一个同步系统,以实现发送端和接收端的同步,因此同步提取在通信系统中是至关重要的。一个简单的接收系统框图如图1所示。

本文引用地址:https://www.eepw.com.cn/article/189783.htm

本文介绍一种基于现场可编程门阵列(FPGA)的同步方案。FPGA是与传统PLD不同的一类可编程ASIC,它是将门阵列的通用结构与PLD的现场可编程特性结合于一体的新型器件,最早由美国Xilinx公司于1985年推出。FPGA具有集成度高、通用性好、设计灵活、开发周期短、编程方便、产品上市快捷等特点,它的门数可达100万门以上。近年来,FPGA在系统的硬件设计方面得到了广泛的应用。

1 同步序列码

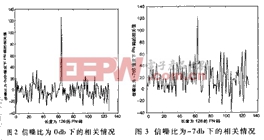

本文介绍的帧同步提取是在每一帧的前面加扩频码,该扩频码必须具有良好的自相关性和互相关特性。表1是m序列码和Gold系列码的性能比较,从表中可以看出,m序列码的自相关性和互相关特性要比Gold系列码好得多,m序列码作为同步头具有较强的抗干扰能力和较低的截获概率,而且长的m序列更容易在一定的强噪声中被提取,这样就能够充分保证数据的正常通信。因此相对于Gold系列码来说,m序列码更适合于作为同步头。本文的同步序列码指的是M序列码,M序列码是由m序列码得到的,即在相应的m序列码后补零,用以实现PN码的相等匹配,因为对应m序列码来说,1的个数总是比0的个数多一个。 利用相关法,在同步头没有来临之时,其相关峰比较低;如果数据中的同步头和本地同步头完全对齐,那么就能够出现大的相关峰值,但这个峰值可能不会达到理论值,这是因为在数据传输中,数据流包括同步头都要受到噪声的干扰。因此,同步提取还要看同步是在一个什么样的噪声环境中才能良好工作。本文介绍的是长度为128的M序列码作为同步头的同步提取方法。之所以取长度为128的PN码作为同步信息,一方面是考虑到同步提取的复杂性要求同步信息不能太长,另一方面是要满足相关峰值尽可能的大,长度为128的PN码可以提供21dB的处理增益,这使得在一定的噪声背景下仍然可以提取到相关峰值。 图2是在信噪比为0dB下的相关情况。可以看出在0dB下长度为128的M序列码作为同步头的相关特性是良好的。图3是在信噪比为-7dB的情况下做的仿真。可以发现,由噪声所产生的相关峰增高,有超过最高相关峰的趋势。经过实验,信噪比继续降低时,真正的相关峰就会被噪声所产生的相关峰淹没,这样就不能提取出相关峰。因此,同步提取要考虑噪声的影响。

评论