基于FPGA的微电网并网控制器的设计与实现

摘要:针对微电网与大电网能量交互的问题,设计了一种基于现场可编程门阵列(FPGA)实现的微电网并网控制器。该并网控制器以ADS7864芯片为核心实现数据的的同步采样;同时,根据锁相原理,研究了一种改进的基于同步空间坐标变换的锁相控制算法,给出了锁相环模块中滤波器和PI调节器参数的设汁方法。通过Matlab/Simulink仿真分析验证了锁相环的有效性,最后研制出基于FPGA实现的并网控制器并应用于微电网实验平台。实验表明该控制器能实现快速准确的数据采集和锁相控制,从而实现微电网的平滑并网。

关键词:微电网;控制器;并网;现场可编程门阵列

1 引言

微电网是智能电网的一个重要发展方向,能很好解决单个分布式发电单元独立接入给大电网造成的不稳定,从而为大电网提供有力的支撑。

微电网中的并网控制器主要由同步数据采样模块、数字锁相模块和并网算法模块构成。基于文献,在此设计了一种改进的基于同步坐标变换的动态锁相环,该锁相环能消除电网电压幅值波动带来的影响,从而有效克服零点检测法、静止坐标系法和普通同步坐标变换方法的不足。

首先介绍了并网控制器的总体设计,然后对并网控制器的数据采样模块、锁相控制模块和并网算法模块进行详细分析。最后研制出基于FPCA实现的并网控制器,实验证明所设计的并网控制器能较好地实现微电网的并网控制。

2 系统总体设计

所设计的并网控制器由同步数据采样模块、数字锁相模块和并网算法模块构成。12位六通道低功耗高速同步采样芯片ADS7864负责数据的同步采集,FPGA负责整个系统的驱动控制,主要包括数据采样模块的驱动、数字锁相算法的实现及并网控制算法的实现。系统工作原理:同步采样模块实时采集电网侧和微电网侧母线电压;FPGA根据采样信号结合所提出的锁相算法对电网侧和微电网侧的电压进行锁相控制;并网算法模块根据并网条件进行判断,当满足并网条件时发出并网命令完成微电网并网。

3 关键技术研究

3.1 同步采样模块设计

数据采集原理:采用ADS7864芯片实现电网侧和微电网侧电压采集,芯片基准电压为2.5 V,输入电压范围为0~5 V。A/D转换结果y与输入模拟信号量x之间的关系式为:y/4 096=(2.5-x)/5。

采样电路的设计:分压电路拓扑结构如图1所示,图中,利用串联电阻分压,然后通过求差电路将差分线电压转换成单端电压值,并引入箝位二极管防止电压过大损坏芯片。其中R=390 kΩ,R0=110 kΩ,R1=R2=30 kΩ,R3=R4=9.1 kΩ。

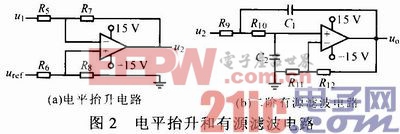

ADS7864芯片的输入电平范围为0~5 V,而采样信号为正弦交流信号,采用减法器电路实现电平的抬升。抬升电平参考电压uref由ADS7864芯片提供,电平抬升电路如图2a所示,其中R5=R6=R7=R8=22 kΩ。

采用二阶有源低通滤波电路对采样信号进行滤波处理,滤波电路结构如图2b所示。其中R9=R10=R11=10 kΩ,R12=0,C1=C2=5.6 nF,该滤波器对信号的放大倍数A=1+R12/R11=1,截止频率fc=1/![]() 。

。

评论