2D-DCT的FPGA实现

在信息社会迅猛发展的21世纪,多媒体信息日益增多,其中人类主要依靠图像来接收各种各样的信息。图像中包含如此巨大的数据量,如果不经过压缩,不仅超出了计算机的存储和计算能力,而且无法完成信息的实时传输。图像的高速传输和所需巨大的存储容量已成为数字图像通信的最大障碍。离散余弦变换(DCT)由于其变换特点被认为是性能最接近K—L变换的准最佳变换,现在已经是最流行的图像压缩变换技术,并已经在JPEG、MPEG-1/2/4、H.26x等国际编码标准中获得了广泛的应用[1].由于集成电子技术的高速发展和广泛运用,数字图像处理也由软件向硬件过渡并得到了非常迅速的发展。FPGA作为当今运用极为广泛的可编程逻辑器件,也是数字图像处理的理想器件。目前,利用FPGA进行图像处理主要是直接在FPGA上利用硬件描述语言或EDA软件进行设计,这种设计方法的最大优点就是速度快,可以利用流水线实现,具有一定的灵活性。

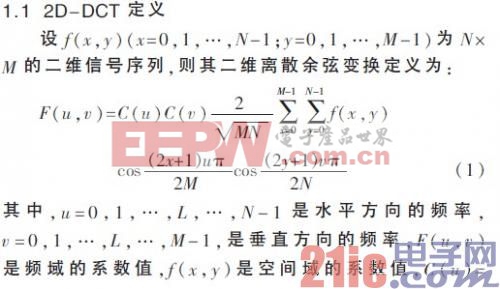

基于行列分解的2D-DCT由于算法规律性强、实现结构直观、时序控制简单而被广泛应用。本文提出使用行列分解法和分布式算法来实现2D-DCT,可以减少硬件资源,提高运算速度,具有一定的现实意义。

1 2D-DCT系统模块设计

离散余弦变换经常使用在信号处理和图像处理中,用于对信号和图像进行有损数据压缩。这是由于离散余弦变换具有很强的“能量集中”特性,使图像的主要信息集中在变换后的低频上,并且能够去掉像素间较强的相关性,让图像的信息集中在少数几个系数上,以减少冗余达到对图像进行压缩的目的。

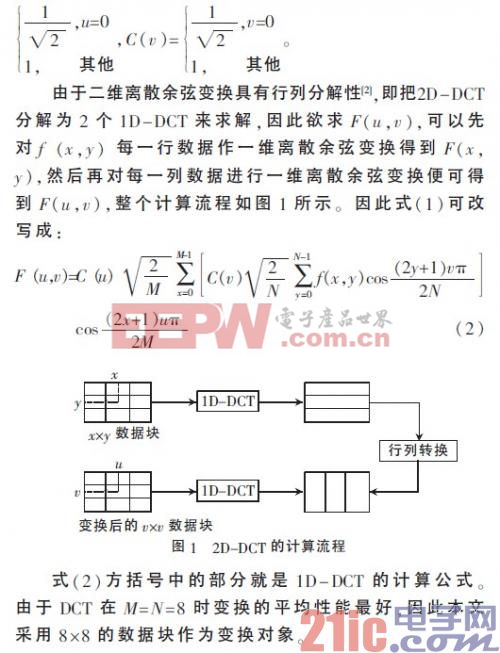

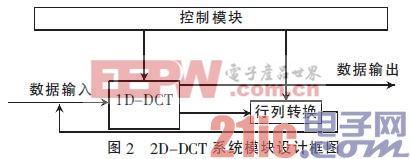

1.2 系统模块设计

根据2D -DCT 的行列分解性及2D -DCT 的计算流程所设计的系统框图如图2 所示, 整个系统由控制模块、1D-DCT 模块和行列转换模块3 个模块组成。

在每个时钟的上升沿从数据输入端输入一个数据,8 个时钟周期后, 输入的就是8×8 数据块的一行数据。同时, 控制模块给1D-DCT 模块一个信号, 通知它对这8 个数据进行1D-DCT 变换, 并且在计算完之后把结果存进行列转换模块中。如此反复8 次后, 就对8×8 数据块完成了行变换, 所得到的64 个数据依然是以8×8 的矩阵形式存放在行列转换模块中。之后控制模块分8 次从行列转换模块中读出8×8 矩阵的每一列数据, 再送入1D-DCT 模块中进行变换, 变换后的数据就是8×8 数据块的2D-DCT 变换结果。

评论