基于FPGA的心音信号采集系统设计

目前,心血管疾病的诊断主要分为无创诊断和有创诊断法两种。其中,无创诊断包括心电图、动态心电图和心音图、超声心动图以及现代医学成像技术[1];有创诊断主要指动脉造影技术,但是会带来并发症。非常严重的心血管疾病并不能够通过心电图做出正确诊断,而早期的心脏病变会引起心音信号成分的变化,通过心音图分析心音成分以及杂音,能对早期心血管疾病做出正确诊断。心音信号是一种非常微弱的随机信号,在采集过程中不可避免地引入了噪声。韦哲等人设计了基于声卡的心音信号采集与处理系统[2],该系统充分利用了计算机资源,但是电脑本身存在较大噪声,采集到的信号信噪比较低。童英华设计了基于单片机的心音、脉搏信号采集系统[3], 但是单片机存在传输速率低的问题。本文设计了基于FPGA的心音采集系统,该系统采集到的心音信噪比较高,适宜后续研究。

本文引用地址:https://www.eepw.com.cn/article/189675.htm1 采集系统整体方案设计

本采集系统框图如图1所示,该系统由心音传感器、信号预处理电路、A/D转换电路以及PC等构成。其中,信号预处理电路首先对心音信号进行前级放大,然后经过带通滤波(由低通滤波电路和高通滤波电路构成),最后经过后级放大电路处理。带通滤波电路可以通过开关控制,前级放大的输出可以通过开关控制直接跳过带通滤波电路直接到后级放大电路,由于前级信号只将心音信号放大到几百毫伏,信号仍然很弱,因此再经过后级放大电路把心音信号放大至+5 V范围内,然后输出到A/D转换电路。A/D转换电路采用8 bit、32 MS/s模数转换单芯片AD9280,A/D转换后的数据直接传送给FPGA,FPGA通过串口将数据实时发送到PC,实现整个采集系统。

2 采集系统实现

2.1 心音传感器的研究

心音传感器是整个系统中的重要部分,它的特性对采集到的信号质量至关重要。本文设计了一款优质、廉价的基于驻极体电容话筒的心音传感器。该传感器灵敏度高,抗干扰能力强,除了能提取出微弱的心音信号外,还能尽量不受外界噪声的干扰[4]。本传感器由一个微型驻极体话筒和一个听诊器的听头组成,听诊器选用的带双面探头的欧石130 K。制作时把听诊器的胶管截去,留下约10 cm左右,该传感器对心音的灵敏度比较高,对外界的声音几乎无反应[5]。振膜接收到声波后发生相应的振动,同时引起极板间距离的变化,电容计算公式为:

其中,ε 为电解质常数,S 为极板表面积,d 为极板间距离。由式(1 ) 可知, 当电容作相应变化时, 由于R 阻值很大, 充电电荷Q 来不及变化, 从而引起电容两端的电压发生变化, 即:

U=Q/C (2 )

这样, 话筒就将声音信号转换成了电压信号。

2.2 心音信号预处理电路

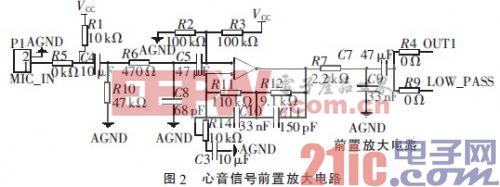

2.2.1 心音信号前置放大电路设计

传感器输出的心音信号微弱并且夹杂着噪声, 为了提取出有用信号, 必须进行放大和滤波处理。本文采用同相输入电路, 并且输入电路需满足如下要求:

(1 ) 前置级的输入阻抗要足够高, 从而保证心音信号的稳定放大。心音信号源本身是一种微弱的振动源, 将声波转换为电信号的过程又呈现出高内阻特性[ 6 ] , 粗略估计, 与放大器输入端相连的信号源内阻高达100 kΩ。

(2 ) 高共模抑制比(CMRR) 。生物电放大器的CMRR值一般要求达到60 dB~80 dB。但是放大器前边传感器系统影响了它的实际共模能力, 使得共模干扰转化成差模干扰, 降低了整个前置级的CMRR。但是通过提高放大器的输入阻抗可以减小这一转化, 从而保证高的共模抑制比。

(3 ) 低噪声、低漂移。由于心音信号幅度较低, 仅在毫伏级, 并且夹杂着较大的热噪声, 要让输出信号具有较高的信噪比, 就要求放大器的内部噪声较低。为了满足实验需要, 选取NE5532 运算放大器, 它是一种高性能低噪声运算放大器。与大多数的标准运算放大器相比,它具有更好的噪声性能, 输出驱动能力和相当高的小信号和电源带宽。前置放大电路前端加了电解电容进行滤波, 允许高频成分通过, 滤掉低频成分。放大电路如图2所示, 放大倍数为1+(R11+R12)/R14。

fpga相关文章:fpga是什么

电荷放大器相关文章:电荷放大器原理

评论