京微雅格重磅之作―新版FPGA/CAP设计套件Primace5

简介

本文引用地址:https://www.eepw.com.cn/article/189497.htm作为国内唯一一家具有完全自主知识产权的FPGA与可配置应用平台CAP(Configurable Application Platform)产品供应商,京微雅格一直在快节奏的改进与产品配套的软件开发环境。最近,新一代FPGA/CAP设计套件Primace5.0正式发布了。Primace5.0完整的支持了基于时序驱动的布局布线实现流程(Timing-Driven PlacementRouting Flow),提高了布局布线的成功率,减少了设计与验证时间。此外,Primace5.0还配套改进了Synopsys SDC兼容的设计约束输入界面, 方便用户更加准确高效的输入时序约束。配合新型的自动寻找最佳实现的优化工具iXplorer,Primace 5.0可以极大的加速用户设计时序收敛过程。为了方便用户准确描述设计,改善RTL 代码质量,Primace5.0新增了RTL Template功能,其中包括了常用的Verilog设计元素。Primace5.0还第一次完整支持了8051MCU的SoC仿真以及时序仿真(Timing Simulation)。相对上一代版本,新一代Primace显著改进了用户信息提示以及流程的稳定性。本文将简要介绍这些改进以及对用户使用体验的影响,并推荐几种可以有效改进设计流程,加速设计过程的方法。

Primace5.0主要新增/改善的功能

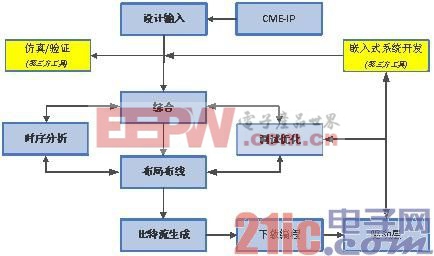

Primace5.0中基本设计流程保持了一贯的简洁的特点,如图1所示,主要包括设计输入(RTL编辑等),设计实现(综合、布局布线等),时序收敛(以静态时序分析为基础的设计、实现调整),以及码流下载和片上调试(DebugWare等)。

图1: Primace中FPGA/CAP开发流程

基于时序驱动的布局布线

时序驱动的布局布线是一种已经被广泛证明与接受的设计方法,设计人员通过描述设计的时序约束(包括核心频率约束,I/O约束,例外约束,特定路径约束,跨时钟域约束等)可以有效指导布局布线程序高效、高质量的完成设计实现。Primace5.0中接受的时序约束包括:

Basic Timing Path

Clock Setup/Hold, Falling edge

Tsu/Th, Tco, Tpd

Advanced Timing Path

False path

Generated clock

User edited sdc

时序约束输入辅助

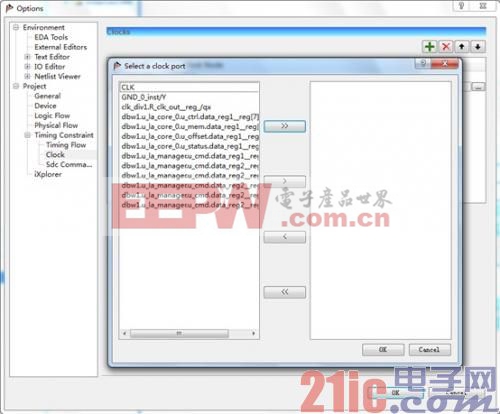

为了方便用户可以准确高效的输入时序约束,Primace5.0还配套改进了兼容Synopsys SDC的设计约束输入界面。如下图所示:

图2: 选择时钟界面

图3:时钟约束设置界面

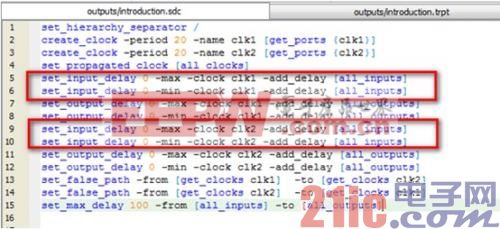

各类SDC最终汇总在统一的SDC约束文件里,用户可以集中编辑:

图4:SDC编辑界面

评论