基于FPGA的手持式示波器设计

摘要:在此设计的低成本手持式示波器是以ADC128S022模/数转换芯片为数据采集前端;使用FPGA片内双口内建RAM进行数据存储、有限状态机实现示波器的触发控制和显示驱动;最后再用LCD12864液晶模块完成终端的低成本图形显示。在DE0-Nano FPGA(Altera Cyclone IV)开发板上的测试结果表明,所设计的手持式示波器可以实现模拟信号任意电平上升沿或下降沿的触发测量;垂直灵敏度和扫描速度调节、波形参数的直接读出等功能。

关键词:FPGA;示波器;液晶显示屏;有限状态机

0 引言

目前,数字存储示波器以其体积小、携带方便、准确率高的独特优势逐步取代了传统的模拟示波器,并向着更为小巧的低成本、便携式应用方向发展。近几年来,许多研究者充分利用FPGA片上的资源丰富、使用灵活、开发成本低的优点提出了一些数字示波器的虚拟仪器解决方案和嵌入式解决方案,这些设计采用FPGA片内资源来实现数字示波器的数据存储(RAM)、触发控制、数字信号运算与处理、显示终端驱动等功能,这在很大程度上能够降低示波器成本和复杂度,但是这些设计方案往往会使用到微处理器(8051/ARM/NoisⅡ)作为系统调度和数据处理的核心或采用VGA显示器作为图形输出终端,还不能达到低成本的手持便携使用要求。

LCD12864液晶显示模块具有低压、微功耗、寿命长、超薄等显著优点,比较适合低成本、便携式电子信息产品来实现字符和图形的显示。因此,文中就以LCD12864液晶模块作为数字示波器的低成本图形显示终端;基于FPGA应用技术,设计出了具有模拟信号任意电平、上升沿或下降沿触发;垂直灵敏度和扫描速度调节、波形参数的直接读出特点的低成本手持式数字示波器。

1 手持式示波器的系统设计

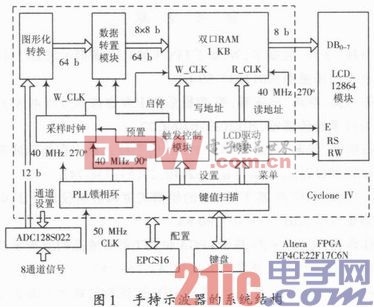

基于FPGA的手持式示波器系统结构框图如图1所示,系统主要包括片外AD芯片、配置芯片EPCS16、以及片内PLL模块、采样时钟配置模块、按键扫描模块、触发控制模块、双口RAM存储模块、采样数据图形化与转置模块、LCD12864显示驱动模块等。示波器的工作过程大致如下:经过片外ADC128S022采集的12 b数字信号,再经过片内图形化模块后转换成1列LCD屏显示的点阵数据;为了适应液晶屏按行读出的工作方式,需要通道数据转置模块把按列采样的点阵数据转置成按行排列的数据;触发模块主要是要根据用户设置(键盘输入)的触发电平及模式来控制RAM的写数据开始或停止指令,同时生成对应的写数据地址;数控采样时钟模块可以产生多种不同的采样时钟以满足不同频率信号的测量显示;LCD驱动模块主要是依据LCD的工作时序产生RAM的读数据地址和LCD模式控制指令。

图1所示手持式示波器的设计关键在于根据LCD12864显示模块的工作时序来组织双口RAM的读/写、片外A/D的数据采集;这样才能保证测量的模拟信号波形显示正确。下文就对片外A/D模块、双口RAM的读写控制和LCD显示驱动3个关键模块做出比较具体的设计描述。

fpga相关文章:fpga是什么

评论