基于FPGA实现异步串行通信

摘要:为了适应全数字化自动控制更加广泛的应用,采用现场可编程门阵列(FPGA)对异步串行通信控制器(UART)进行多模块的系统设计的方法,使串口通信的集成度更高。对UART系统结构进行了模块化分解,可分为三个模块:FPGA波特率发生器控制模块、FPGA数据发送模块及数据接收模块。采用Venlog语言描述硬件功能,利用Xilinx公司的FPGA芯片,在Xilinx ISE Design Suite 13. 4环境下进行设计、编译、综合、下载。采用第三方仿真工具ModelSim进行模拟仿真。

关键字:FPGA;UART;多模块;Verilog;Xilinx ISE

异步串行通信(UART)是一种广泛应用的串行数据传输协议,UART的要求是传输线少,可靠性高而且传输距离远。UART功能负责从总线采集数据,转换成传输格式,然后发送到串口。也负责从串口接收数据,检查和删除附加的位,并传送结果数据给总线。异步串行通信广泛的应用于军事、工业、自动控制、仪器、通信、医药、话音图像处理等众多领域。现实应用中多采用专用集成芯片实现UART功能,如8250、825 0A、16450、16C451、16C551等。但在实际应用中,一般只需要UART的几个主要功能,专用芯片成本比较大且造成资源的浪费。近年来随着电子设计技术的日趋成熟,特别是FPGA在集成度和速度上的大幅提高,可以用一个芯片构成一个复杂的系统。一个芯片就能完成处理计算、通信、控制等多功能,而且成本大幅度降低。根据以上考虑,本文采用FPGA实现UART功能。

1 UART通信原理

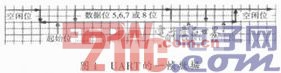

串行通信分为两种类型:同步通信方式和异步通信方式。UART即通用异步串行通信收发器。UART的一帧数据由起始位、数据位、奇偶校验位和停止位组成。数据在传输过程中是通过一个字符接一个字符进行传输来实现通信的。每一帧的信息在传送前传输线处于高电平状态。在传送一个字符信息的时候,每一个字符的接收是靠起始位来同步的,字符的前面是一位起始位,首先发送起始位为低电平,一般用下降沿通知收方传输开始,然后发送起始位之后的数据位,数据位的传送先低位后高位,字符本身由5~8位数据位组成。

数据位后面是奇偶校验位,奇偶校验位后的是停止位,标志着一帧字符结束。停止位后为高电平,为空闲位,并为下一个字符的开始传送做准备。在发送、接收数据时,数据的帧与帧之间如果有间隙,就要在停止位之后附加空闲位,停止位后面是不定长度的空闲位。停止位和空闲位都规定高电平,这样可以保证起始位开始处有一个下降沿。如图1所示。

1. 1 系统设计与硬件实现

异步通信允许在串行链路上进行全双工的通信。本文把异步通信电路作为一个整体来实现,数据接收经过MAX232进行电平转换后经FPGA串口模块的RXD端输入,由FPGA进行串/并转换后,8位有效数据进入总线,再进入处理芯片。数据发送经数据处理后经由总线进入FPGA串口模块,8位有效数据在FPGA中进行并行转换为串行数据后由TXD端输出到MAX232的12管脚,在MAX232种经过电平转换后由TXD端输出,系统基本结构框图如图2所示。

帧格式采用1位开始位,8位数据位,1位停止位,波特率为115 200,根据采用的帧格式,需要发送的数据为10位(1位开始位、8位数据位、1位停止位),在发送完这10位后,就应该停止发送,并使发送端电平处于逻辑1,然后等候下次的发送。

fpga相关文章:fpga是什么

通信相关文章:通信原理

数字滤波器相关文章:数字滤波器原理

评论