基于FPGA实现异步串行通信

1.4 FPGA数据接收模块

数据的接收与数据的发送相比要复杂些。在数据的接收过程中,UART的接收模块首先要进行的是对起始位的检验。一般当接收的第一个是低电平,就标志着一个数据帧的开始,但是在一个数据帧中间也有可能包括一个低电平的位,系统有可能默认为这个低电平为起始位,这样就会产生一个“假的起始位”。所以,在数据接收的过程当中还要包括对数据起始位的判断。所以数据的接收过程可以分为空闲状态、起始位检测状态、数据位读取状态、读取停止状态、准备完成接收和停止位读取状态。在判断起始位低电平后,触发接收过程,进入数据位读取状态使串行总线的输入数据不断被读取并且保存在寄存器内,计数器也到达计数的上限时,接收完成之后并进入准备完成接收状态,UART控制器会在输出结果之前对已经接收的数据进行奇偶校验。然后进入停止位读取状态。在每一种状态,如果使能信号无效时都转回空闭状态。最后UART控制器准备下一次的数据接收并重置控制器内的信号检测器。

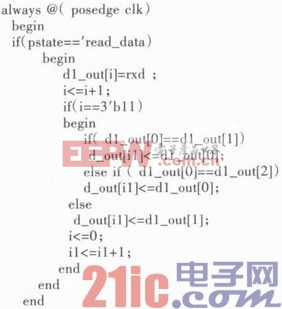

在接收数据过程中,会有一些其他原因使信号产生反转。为了消除毛刺,在接收数据时,采用3选2的方法消除误差。也就是这个字符的值是至少有两次采样的值相等的值。

采用3选2方法接收数据的程序如下:

接收一帧数据的仿真结果如图6所示。本文引用地址:http://www.eepw.com.cn/article/189494.htm

在波特率为115 200情况下对UART进行仿真,结果如图7所示。通过仿真波形可以看出,设计结果正确地发送和接收一帧数据并产生相应的中断。

2 结论

本文介绍了一种基于FPGA实现异步串行通信功能,采用多模块的方法实现异步串行通信功能,可以方便用户根据需要进行裁减、便于理解和调试。本文运用Verilog语言进行设计异步串行并行收发器的IP核电路。

用FPGA实现UART功能,充分利用了FPGA的剩余资源,相对于专用UART芯片,减小系统PCB板的面积,降低系统的功耗,提高系统的稳定性。近年来在电子设计领域中,这种硬件软件化的方法已经成为一种流行趋势。该设计采用Xilinx公司的Spartan3E系列中器件XC3S100E。通过ISE软件进行时序仿真和硬件测试各项通信指标均满足要求,整个设计的正确性和完整性得到验证,各项功能均达到预期的要求。

fpga相关文章:fpga是什么

通信相关文章:通信原理

数字滤波器相关文章:数字滤波器原理

评论