利用单片机和CPLD实现直接数字频率合成(DDS)

直接数字频率合成(DDS)技术是美国学者J.Tierncy,C.M.Rader和B.Gold在1971年首次提出的。这是一种全数字技术,该技术从相位概念出发直接合成所需要的波形。同传统的频率合成技术相比,DDS技术具有很多优点:频率切换时间短、频率分辨率高、相位变化连续、容易实现对输出信号的多种调制等[5]。但是由于当时的技术以及器件水平的限制,它的性能指标还无法与已有的技术相比,因此该技术当时并没有引起足够的重视。最近几年来,随着技术和器件水平的提高,国外一些公司先后推出各种各样的DDS专用芯片,如 Qualcomm公司的Q2230、Q2334, AD公司的AD9955、AD9850等[3]。这些产品的问世,为电路设计者提供了良机,满足了工程实际的需要。然而,商用DDS专用电路芯片也有它的的局限性,并不能满足所有要求。例如,在实现线性调频(LFM)等复杂的调制功能时,利用现有的商用芯片就会遇到一些困难[8]。由于近几年来可编程器件CPLD 、现场可编程门阵列FPGA技术的迅速发展和广泛应用,使用可编程器件实现DDS技术也越来越受到人们的关注。

本文引用地址:https://www.eepw.com.cn/article/172132.htm1 DDS工作原理

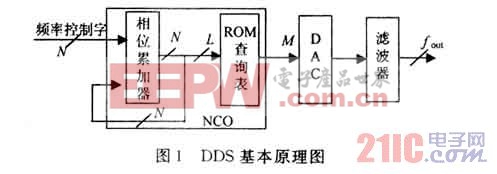

DDS工作原理框图如图1所示,其实质是以参考频率源(系统时钟)对相位进行等可控间隔的采样。由图1可见,DDS包括由相位累加器和ROM查询表构成的数控振荡源(NCO)、DAC以及低通滤波器(LPF)3部分。在每一个时钟周期,N位相位累加器与其反馈值进行累加,其结果的高M位作为ROM查询表的地址,然后从ROM中读出相应的幅度值送到DAC。低通滤波器LPF用于滤除DAC输出中的高次谐波。因此通过改变频率控制字K就可以改变输出频率fout。容易得到输出频率fout与频率控制字K的关系为:fout=Kfc/2N,其中fc为相位累加器的时钟频率,N为相位累加器的位数。定义当K=1为系统频率分辨率,即。

2 系统的总体设计

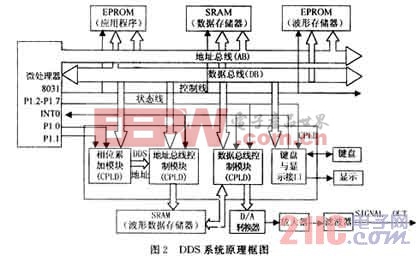

系统的原理框图如图2所示,本系统主要由单片机部分、DDS主通道部分、键盘及显示部分以及输出信号调理等部分组成。

单片机芯片采用的是比较常见的AT80C31芯片。同时片外还各扩展了1片程序存储器2764与数据存储器6264,分别用来存放运行中所需的程序与随机数据。

DDS主通道部分是我们设计的关键所在,该部分主要由相位累加模块、地址总线控制模块、数据总线控制模块与波形数据存储器EPROM、SRAM等组成。其中相位累加模块、地址总线控制模块和数据总线控制模块都是在CPLD上实现,采用的芯片是ALTERA公司的FLEX10K系列器件。我们将所需要合成的波形采样数据固化在EPROM 2764中,但是我们知道EPROM的读周期比较长,很难满足系统的访问时间要求。因此设计中又使用了1片HSRAM,在DDS系统合成波形的过程中,代替ROM进行波形数据的快速查询。

键盘和显示部分是系统和用户进行交互的重要手段。这一部分的逻辑功能,也是在CPLD上实现的。

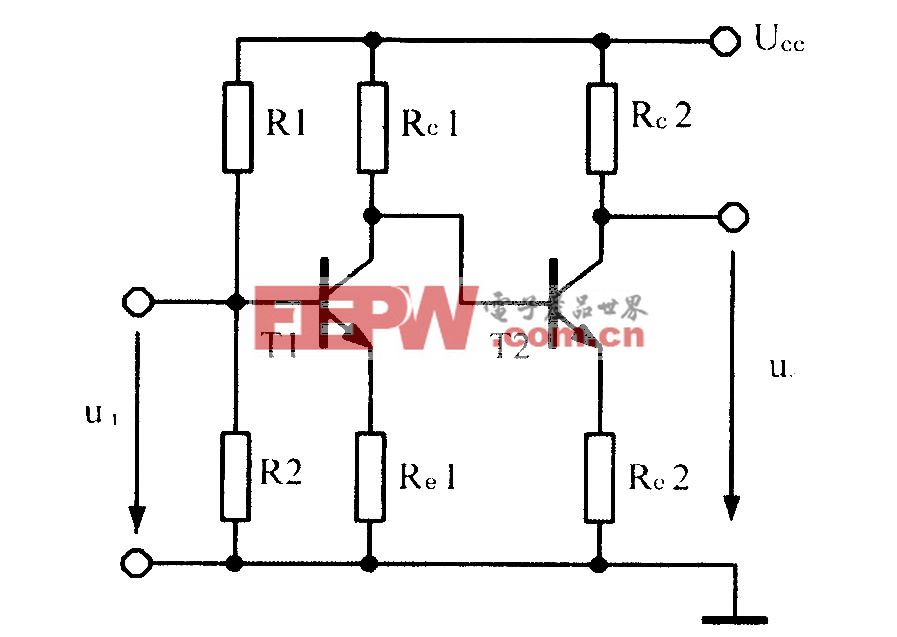

输出信号调理部分是把从HSRAM中读出的波形的数字幅度值首先转换成模拟信号,然后再进行放大、滤波处理后输出。这一部份包括D/A转换器、幅度放大器和滤波器。DAC器件采用AD公司的12位AD9713B,该器件特点是具有较高的更新速率(100 MSPS)和较低的功耗(725 mW)[1],因此特别适合于DDS信号合成。幅度调节电路使用的是双极性放大器AD708、AD9617和AD9713所组成的电路。

3 系统总体工作状态说明

前面已经提到过,由于EPROM的读取时间比较长,很难满足系统对时间的要求,因此在系统中又增加了1片高速SRAM,作为波形数据缓存器。这样,系统就有两个工作状态:首先,系统开始工作时,需要将波形数据从EPROM调到HSRAM中,即波形数据的加载状态;数据加载完毕后,按照DDS合成原理进行信号合成,即信号的合成状态。系统设计中使用单片机的P1口控制这两种工作状态之间的切换。

3.1 波形数据的加载

单片机系统上电自检完毕后,开始进行波形数据加载过程。此时,地址总线控制模块和数据总线控制模块,将总线的控制权交给单片机系统。在该过程中,EPROM处于读状态,而SRAM为写状态。8031 按照EPROM、SRAM的时序要求,将8 k的波形数据从EPROM加载到HSRAM中。该过程大概需要几毫秒时间。

由此我们知道,用这种方法不仅能够合成标准波形(如:正弦波、方波、三角波等),而且还可以合成各种非标准波形。对此我们只要通过数据采集器或PC机获得8 K的波形数据,然后存入到EPROM中,就可以按所需要的频率输出相应波形。

3.2 波形合成电路的设计

当波形数据加载完毕后,系统就可以进行信号合成。单片机将接收到的频率值转换成频率控制字,送到相位累加器。相位累加器在每一个时钟周期进行相位累加,然后将每次的累加和作为地址去寻址SRAM,读出与该地址所对应的波形幅度值,然后送到D/A转换器转换成模拟信号,最后经幅度放大、滤波输出。

评论