单片机系统中高速数据采集的实现

在单片机系统中通常要用到高速数据采集。虽然目前单片机的工作频率不断提高,但仍然无法满足如周期信号频谱分析等需要采用高速数据采集的场合。对于速率在l00 kS/s以上的数据采集,如果采用一般的中断查询法就不易实现,因此可考虑通过存储器直接存储转换数据来实现1 MHz以上的高速数据采集。

本文引用地址:https://www.eepw.com.cn/article/172131.htm1系统结构

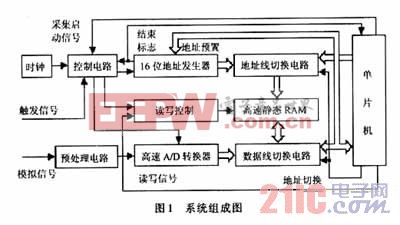

系统由单片机、高速A/D转换器、高速静态RAM及切换控制电路等部分组成,如图1所示。静态RAM用作单片机与A/D转换器之间的数据缓冲。

RAM的数据线和地址线由总线切换电路来控制,选择连接单片机总线或连接到A/D转换器的数据输出和地址发生器输出地址。RAM的读写由读写控制电路实现。

在数据采集期间,存储器的写入地址由可预置的16位地址发生器产生,其溢出信号作为数据采集结束控制。

图1中单片机采用89C5l;静态RAM由2片CYPRESS公司的高速静态存储器CY7Cl9920构成64 k的存储器,典型读写时间20 ns;转换器采用MAXIM公司的流水线型高速A/D转换器MAXl426, 采用循环采集方式;总线切换采用74F245三态总线收发器并联方式,典型传输时间为65 ns;地址发生器是由4片计数器74Fl63级联组成的可预置数的16位二进制计数器,可以预置16位地址的初值,也就是传输数据块的起始地址。一片 74Fl63的典型传输时间是65ns,所以地址发生器的延时时间为26 ns。

2原理与设计

2.1数据采集

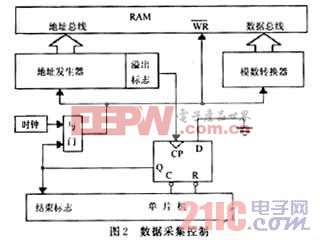

数据采集控制电路如图2所示。系统开机运行时或进行内部数据处理时应把D触发器清零,使数据采集电路处于禁止状态。当单片机完成初始化或准备就绪后,首先向地址发生器写入数据块的起始地址,并把总线切换控制线置位,把RAM的控制权交给采集电路。置位D触发器开始数据采集,然后等待数据采集结束。在数据采集过程中,单片机也可以通过对D触发器清零强行中断数据采集。当采集数据写满静态RAM时,地址发生器发出一个溢出脉冲,使D触发器清零。D触发器的输出经与门使地址发生器和A/D转换器停止工作,并同时通过结束标志通知单片机。

2.2总线控制

总线的选择控制是由2组74F245三态总线收发器完成。2组总线收发器一端接至静态RAM的地址总线和数据总线,另一端则分别接单片机总线和地址发生器的地址输出与A/D转换器的数据输出构成的外部总线。在数据采集期间,选通外部总线,由A/D转换器把采集到的数据直按写入到静态RAM中保存。当数据采集结束后,选通单片机系统总线,由单片机对静态RAM中的数据进行运算处理。数据总线是8根,故需要2片74F245对数据线进行切换;而地址线有l6根,则需要4片74F245对地址线进行切换。

2.3数据传输

时钟信号的占空比为05,经过与门之后输出到地址发生器、A/D转换器和静态RAM的写控制端。地址发生器设计为上升沿触发方式,A/D转换器 MAXl426也是上升沿开始转换。故当上升沿到来时,地址发生器把地址加1形成新的地址。同时,A/D转换器进行模数转换。当时钟下降沿到来时,A/D 转换器的输出数据已稳定的放到了数据总线上,故下降沿将他写入到静态RAM的新地址中。由于74F245的典型传输时间为6.5 ns,故地址发生器的延时时间是26 ns。而A/D转换器MAX1426的最高时钟频率为10 MHz,故从开始转换到数据稳定输出的最短时间为50 ns,所以地址发生器完全能够满足要求。

评论