异步FIFO和PLL在高速雷达数据采集系统中的应用

随着雷达系统中数字处理技术的飞速发展,需要对雷达回波信号进行高速数据采集。在嵌入式条件下,要求获取数据的速度越来越快。精度越来越高,以致数据量及处理速度要求大增。为避免数据处理不及时,发生数据丢失,影响系统可靠性,要进一步提高系统实时性,必须研究开发高速嵌入式雷达信号采集系统。这里结合高速嵌入式数据采集系统,提出一种基于CvcloneⅢFPGA实现的异步FIFO和锁相环(PLL)结构来实现高速缓存,该结构可成倍提高数据流通速率,增加数据采集系统的实时性。采用FPGA设计高速缓存,能针对外部硬件系统的改变,通过修改片内程序以应用于不同的硬件环境。由于FPGA可重配置,可通过对其编程修改其电路功能,方便后续的系统升级。

2 高速雷达数据采集系统结构

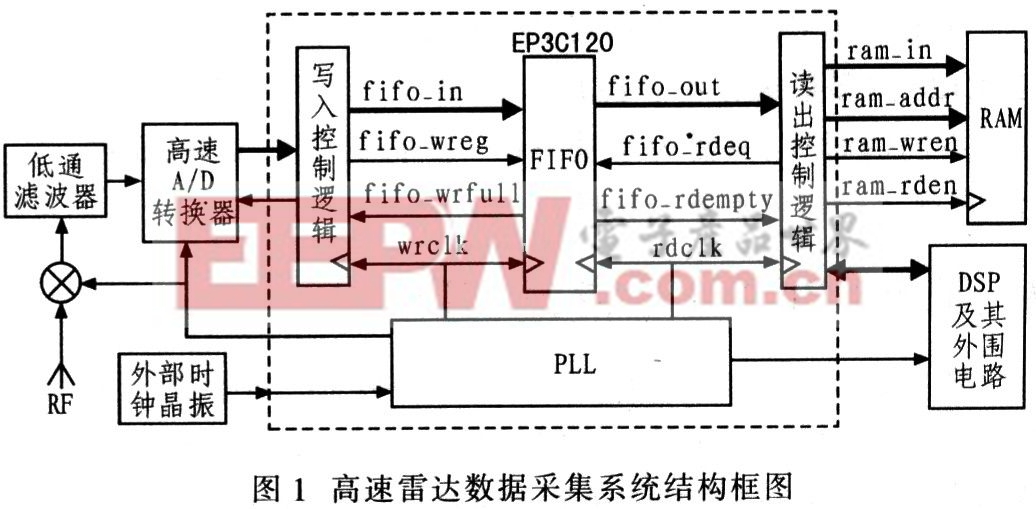

图1为高速雷达数据采集系统结构框。

通过下变频将接收的射频信号变换为适合A/D采样的中频信号。再经A/D转换器转换为数字信号,然后FPGA中异步FIFO构成的高速缓存将中频采样数据变换为与存储器写时间相匹配的低速数据并存储到RAM中。DSP及其他数据处理器通过与RAM或FIFO间进行数据传递,分析处理雷达回波信号,就可获取信号的特征和特征参数。如果DSP不通过缓存而直接与A/D相连,在采样过程中,若A/D连续采样数据,DSP一直处于连续的间隔读数状态,这将占用DSP大部分处理时间,导致DSP不能进行其他工作。也可能出现上一次的数据还没被DSP处理完,下一次采集过程就开始的情况。如果选取更高速的A/D转换器,甚至会发生数据丢失,破坏系统的可靠性。同时由于DSP不直接与A/D转换器相连,所以A/D转换器的升级或替代都不会影响原来的数据采集系统,且使用高速缓存后数据采集速率可达所采用的A/D转换器输出的最高速率,能充分发挥DSP算法处理功能强大、速度高的优势。而采用CycloneⅢFPGA设计高速缓存,设计灵活、通用性强。整个系统具有实时性高、体积小、开发周期短、易于维护和扩展、适于实时信号处理等多个优点。高速雷达数据采集系统的设计主要包括高速A/D转换电路、读写控制逻辑电路、由双时钟FIFO构成的高速缓存电路、锁相环、外部有源品振等,尽量选用高速器件以提高数据采集系统的瞬时带宽和存储深度。

高速A/D转换器采用MAX101A,其最高采样速率可达到500 Ms/s,采样精度为8 bit,该器件属于直接转换式模数转换器即Flash A/D转换器,其特点是速度快,内置1.2 GHz带宽的采样保持放大器,特有的量化设计使其具有较好的动态特性。如果采集系统需更高的采样速率,可使用多片A/D交替采样。FPGA采用EP3C120,EP3C120利用65 nm低功耗工艺,不但实现低功耗,还具有丰富的逻辑(120 KB逻辑单元)、存储器(高达4 Mbit),及数字信号处理资源(288个DSP乘法器)。EP3C120的低功耗特性和其大容量的存储器使其非常适合嵌入式高速雷达数据采集系统设计。采用异步FIFO构成的高速缓存即是使用FPGA巾高达4 Mbit容量的存储器。由于该器件具有乘法器,可辅助DSP器件完成一些计算密集型的算法。

由于一般采用品振作为时钟源,通过上下变频得到各个单元需要的时钟,但这又提高了系统的复杂度。这里采用CycloneⅢ系列FPGA可方便地解决此问题.EP3C120内部集成有4个PLL单元,各个PLL可为不同模块提供不同的时钟,只需为系统提供一个高稳定的晶振,通过PLL单元进行时钟上下变频即可。

3 基于FPGA实现异步FIFO设计

异步FIFO是在两个相互独立的时钟域下,数据在一个时钟域写入FIFO而在另一个时钟域又从该FIFO中将数据读出。异步FIFO通常被用来将数据从一个时钟域安全地传送到另一个时钟域。FIFO可作为A/D转换器件和DSP间的桥梁。使用FIFO作为输入缓冲,由A/D转换器件把采样转换的值同步写入FIFO,每写入一块数据便向DSP发出一个信号,以提醒DSP从FIFO中读取数据块。这样比单次读的效率要高的多,不会有数据丢失,且仅占用少量的系统资源。设计一个异步FIFO,读写使能由不同的时钟激励控制输入和输出数据,空/满标志既用来防止数据的上溢和下溢,也作为写入/读出控制逻辑的输入信号,用来控制A/D数据采样过程和对DSP数据的传输。当FIFO输出满标志时,写入控制逻辑停止A/D采样,等待满标志无效时恢复数据采样。从而防止数据丢失。当FIFO输出空标志时,读出控制逻辑停止DSP的数据读取,等待空标志无效时恢复数据读取。图1中FPGA内的写入/读出控制逻辑使用有限状态机设计,有限状态机能有效的进行读写时序控制,根据A/D和处理器的时序控制原理画出状态转移图,进行编程设定。

FIFO的参数指标直接影响数据采集速度。首先,FIFO的读写速度要足够快,其工作频率至少要大于等于A/D转换器件的采样率,才能充分发挥A/D转换器件的高采样率并保证无数据丢失。其次,FIFO的存储容量要适宜,容量过大会造成资源浪费,容量过小会造成溢出或数据采集速度过慢。系统FIFO采用EP3C120实现。由FPGA实现异步FIFO时,可方便的根据A/D转换器的采样精度和DSP数据宽度设计FIFO的输人数据宽度和输出数据宽度,且采用PLL设计后,可方便的调整FIFO写入端和读出端的时钟频率,使FIFO设计的高速缓存具有一定的通用性。异步FIFO是在QuartusⅡ开发环境下利用其IP核设计的,该设计的异步FIFO可支持高达256位的数据宽度;支持存储的最大深度可达131 072words,同时支持空满标志位。表1给出系统在不同存储深度时消耗FPGA片内资源的情况。可见,针对不同的数据采集需求,可利用Ahera公司提供的参数化的IP核方便的选择FIFO的数据位宽度及存储深度,避免资源浪费。

评论