因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。 什么是PL

关键字:

PLL

简介市场对更高带宽和更高数据速率的需求日益增加,系统频率和调制速率要求不断提高。随着曾经用于军事和国防领域的应用进入消费市场,低功耗变得至关重要。在满足这些要求的同时,还需要保证:不会牺牲电气性能或功能。为了满足这些要求,除了改善进信噪比(SNR)、误码率(BER)和用户熟悉的优质服务外,还必须改善本地振荡器(LO)的相位噪声。 新推出的 ADF5610 是一款集成式锁相环(PLL)和压控振荡器(VCO),充分体现了ADI致力于解决这些问题最终取得的成果。频率覆盖范围ADF5

关键字:

SNR LO VCO LUT PLL

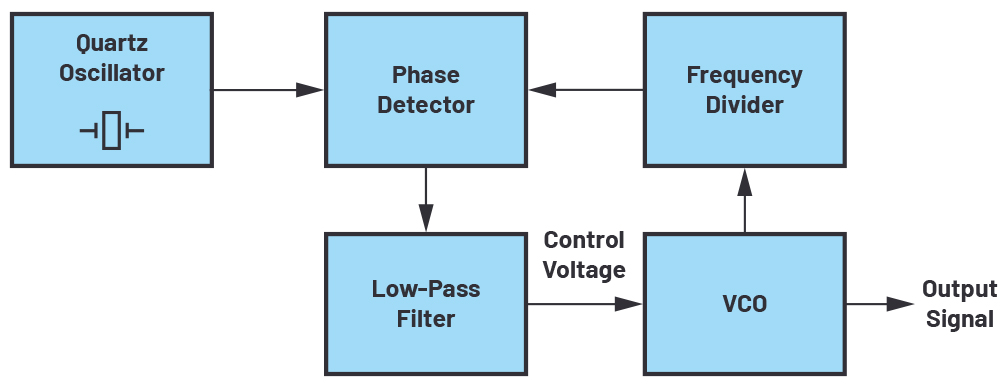

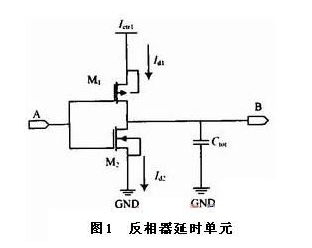

锁相环(PLL)电路是由压控振荡器(VCO)和鉴相器组成的反馈系统,振荡器信号跟踪施加的频率或相位调制信号是否具有正确的频率和相位。需要从固定低频率信号生成稳定的高输出频率时,或者需要频率快速变化时,都可以使用PLL。典型应用包括采用高频率、电信和测量技术实现滤波、调制和解调,以及实现频率合成。图1所示为基于PLL的频率合成器框图。VCO生成输出信号。通过PLL将其保持在设定频率,并锁定到基准频率。基准频率通常由非常精准的石英振荡器提供。在锁相环电路的反馈路径部分,在鉴相器前通过分频器提供可调的VCO分频

关键字:

VCO PLL

系统采用三相半桥拓扑,以STM32F407ZET6单片机为主从控制器,主控制器在dq坐标下进行控制实现三相稳压输出,从控制器采用主从均流控制实现两台三相逆变器的电流分配,采用三相同步锁相环(SRP-PLL)。逆变器单独工作时,输出交流母线电压为24.01 V,频率为49.99 Hz,总谐波畸变率为1.63%,系统整体效率为92.33%,负载调整率为0.12%。逆变器并联工作时,系统实现了两台逆变器输出功率比可调,输出线电流折算值误差最大值为0.06 A,并联工作负载调整率为0.21%。此外,系统具有友好的

关键字:

三相逆变器 主从均流 SPF-PLL 201809

PLL(Phase Locked Loop): 为锁相回路或锁相环,用来统一整合时脉讯号,使内存能正确的存取资料。PLL用于振荡器中的反馈技术。锁相环通常由鉴相器(PD)、

关键字:

PLL 振荡器 DCDC

功率分析仪在测试时出现的数据跳动、效率异常等现象,很多时候与信号的频率是否准确测量有着很大的关系,本文就对频率测量的重要性进行分析,希望能帮助大家进行更准确的测量。 首先我们来看看为什么频率的测量对其他参数会造成如此大的影响。 同步源的选择 用过功率分析仪的工程师一定会记得,在对仪器进行设置的时候,一个叫“同步源”的设置选项,该选项包括了各个测试通道的电压和电流,工程师可以自主来进行选择。该选项的选择对直流信号测试影响不大,但对交流信号的测试会有很大的影响。原因是因为如果交流信号测量数据的间隔如

关键字:

PLL 频率

1 频综布局 单频综布局。通常采取如图形状进行布局:左臂支为参考频率源及锁相环控制电路,右臂支为压控制振荡器(VCO)输出隔离放大电路。中部环状为锁相环(PLL) 乒乓切换式频综布局,又叫音叉式布局:音叉的两臂为对称两个 PLL 频综,臂交汇点为开关切换装置。公共臂为切换后输出放大两路。 多通道收发接收机或者发射机本振电平分配电路布局:对称树状布局。 2 混频器(MIXER)电路布局 混频电路又称上下变频电路,是发射机和超外差式接收机的重要组成部分,是一种典型的频谱搬移电路。对于接收机来讲,

关键字:

射频,PLL

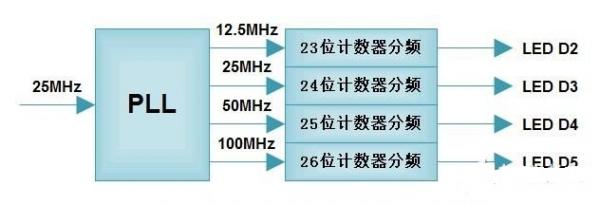

如图8.17所示,本实例将用到FPGA内部的PLL资源,输入FPGA引脚上的25MHz时钟,配置PLL使其输出4路分别为12.5MHz、25MHz、50MHz和100MHz的时钟信号,这4路时钟信号又分别驱动4个不同位宽的计数器不停的计数工作,这些计数器的最高位最终输出用于控制4个不同的LED亮灭。由于这4个时钟频率都有一定的倍数关系,所以我们也很容易通过调整合理的计数器位宽,达到4个LED闪烁一致的控制。

cy4.v模块代码解析 先来看cy4.v模块的

关键字:

FPGA PLL

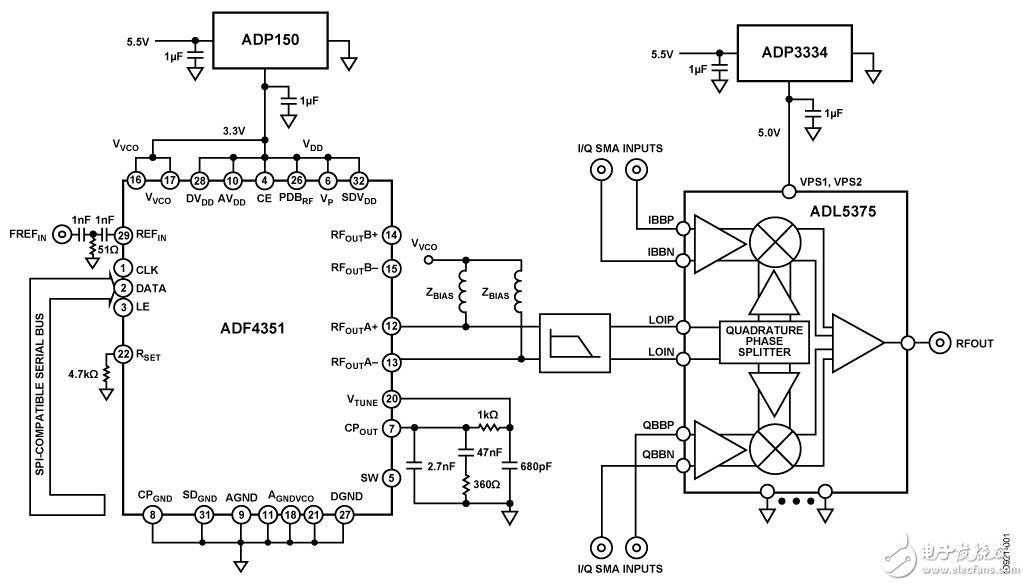

宽带低误差矢量幅度(EVM)直接变频发射机原理图-本电路为宽带直接变频发射机模拟部分的完整实现方案(模拟基带输入、RF输出)。通过使用锁相环(PLL)和宽带集成电压控制振荡器(VCO),本电路支持500 MHz至4.4 GHz范围内的RF频率。对来自PLL本振(LO)进行谐波滤波,确保提供出色的正交精度、边带抑制和低EVM。

关键字:

VCO PLL ADI 变频发射机

利用可编程振荡器增强FPGA应用-可编程时钟振荡器用作FPGA系统的时序参考,可提供一系列优势。其中首要优势是为了实现时钟树优化而进行高分辨率频率选择时所带来的设计灵活性,另一个巨大优势是具有可以减少电磁干扰(EMI)的扩频调制功能。

关键字:

DLL PLL FPGA

PLL和DLL:都是锁相环,区别在哪里?-一般在altera公司的产品上出现PLL的多,而xilinux公司的产品则更多的是DLL,开始本人也以为是两个公司的不同说法而已,后来在论坛上见到有人在问两者的不同,细看下,原来真是两个不一样的家伙。

关键字:

锁相环 DLL PLL

PLL锁相环的特性、应用与其基本工作过程-PLL(Phase Locked Loop),也称为锁相环路(PLL)或锁相环,它能使受控振荡器的频率和相位均与输入参考信号保持同步,称为相位锁定,简称锁相。

关键字:

pll 锁相环

PLL锁相环的基本结构及工作原理-PLL(Phase Locked Loop): 为锁相回路或锁相环,用来统一整合时脉讯号,使高频器件正常工作,如内存的存取资料等。PLL用于振荡器中的反馈技术。 许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步。

关键字:

pll 锁相环

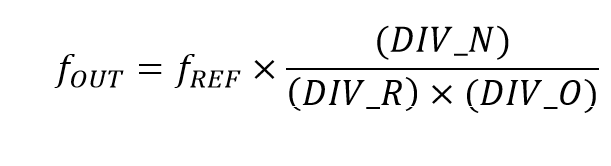

时钟设备设计使用 I2C 可编程小数锁相环 (PLL),可满足高性能时序需求,这样可以产生零 PPM(百万分之一)合成误差的频率。高性能时钟 IC 具有多个时钟输出,用于驱动打印机、扫描仪和路由器等应用系统的子系统,例如处理器、FPGA、数据转换器等。此类复杂系统需要动态更新参考时钟的频率,以实现 PCIe 和以太网等其它诸多协议。 时钟 IC 属于 I2C 从器件,需要主控制器来

关键字:

I2C PLL

pll介绍

魔方之PLL

PLL,(Permutation of Last Layer),魔方速度还原法CFOP的最后一步,是将最后一层的方块移动到正确位置的一步。共有21个公式。(还有其他版本)

---------------------------------------------------------------------------------------------

PLL( [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473