基于PCI IP核的码流接收卡的设计

本文介绍了一种基于Altera公司的PCI接口IP核的DVB码流接收系统的硬件设计方案及设计要点的分析。该设计采用Altera公司的新一代FPGA芯片EP1C12和PCI IP核以及高速串行数据通信接收芯片,实现DVB-ASI信号的接收。

关键词:DVB;异步串行接口;PCI;IP核

前言

随着数字化广播电视技术的迅速发展和基于MPEG-2标准的图像压缩和复用技术的完善,利用PC对大容量信息的处理变得日益重要,如基于PC的软复用器的实现,使得通过PC接收DVB(数字视频广播)码流已逐渐成为一项不可替代的多媒体数据接收技术。因此,设计基于PC平台的DVB 码流接收卡是数字广播电视发展的需要。

由于DVB-ASI信号的平均传输速率为270 Mbps,而DVB传输流又要求保证接收的实时性,因此本文选择了PCI总线。33MHz、32位的PCI总线的数据传输速率最高可达133MBps, 完全可以满足高速实时传输的需求。选择了Altera公司的PCI编译器软件包来实现PCI接口控制电路。该软件包为PCI接口提供了一个完整的解决办法,包含了PCI控制电路的所有功能。用户可以通过修改参数生成所需的IP核模块,以设计自己的外部设备接口逻辑。本文选择了其生成的PCI_MT32功能模块。

系统硬件模块设计

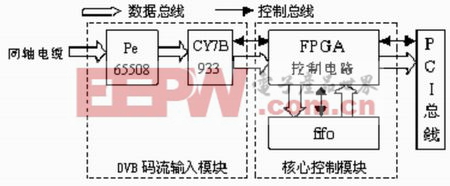

系统的硬件电路设计要求:能将传输速率为270 Mbps的串行DVB—ASI码流实时、无损地通过PCI接口传输到PC,以供PC上的应用程序做进一步处理。在操作和使用上要方便,在设计上要求结构紧凑、接口简单、性能可靠、易于升级。系统硬件框图如图1所示。

从图中可以看出,由于使用了FPGA及PCI IP核,使整个硬件电路显得特别简洁。它主要由DVB码流输入模块和核心控制模块组成。串行DVB传输流经同轴电缆进入DVB码流输入模块,转换为8位并行输出。核心控制模块对并行数据进行缓存,并采用DMA方式传输给PCI总线,完成本地总线和PCI总线的可靠通信。

DVB码流输入模块

本文选用ASI接口。ASI信号由同轴电缆经BNC接头输入,经过互感(用PE65508芯片)转换为PECL(正向发射极耦合逻辑)差分电平信号,再经过耦合电路,到达CY7B933的差分线输入端。 CY7B933是Cypress公司的一种用于点对点高速串行数据通信的接收芯片,它完成码流输入模块的核心功能。它有三种工作模式,这里选用它的解码模式对输入信号进行8B/10B解码和串并转换。最后输出经过字节对齐的8位并行TLL信号,输出的信号包括 MPEG-2传输流和作为同步字使用的逗号字符(在8B/10B传输码规则中定义为 K28.5专用字符),其输出速率恒定为27MBps。

图1 系统硬件框图

核心控制模块

核心控制模块由FPGA控制电路和异步FIFO组成。主要完成对输入ASI信号的缓存和对PCI总线信号的控制的功能。其中最主要的部分是FPGA控制电路。基于整个系统的性能的考虑,选择Altera公司的EP1C12。这款芯片有12060个逻辑单元,52个RAM块等资源,完全可以支持本设计的要求。

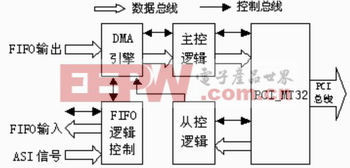

FPGA控制电路内部框图如图2所示,它是本设计的核心部分,对输入的ASI信号保留有效的DVB传输流,发送到FIFO输入端进行缓存。并将FIFO缓存后输出的数据用DMA传输方式通过PCI总线实现对PC内存的存取,同时利用FIFO的标志信号控制DMA传输过程。下面对FPGA控制电路的各模块进行介绍。

PCI_MT32功能模块

本文在选择PCI接口芯片时,选择了Altera公司的PCI 编译器软件包,它可以参数化地生成用于PCI接口的IP核----MegaCore。这个可编译和综合的MegaCore有以下4种宏功能模块:PCI_MT64、PCI_MT32、PCI_T64和PCI_T32。它们都可以完成总线协议的转换,将复杂的、电气和时序要求高的PCI总线逻辑转换为易于操作的本地接口逻辑,遵循PCI总线协议2.2版,经过严格的工业级验证并支持多款优化FPGA。其中,PCI_MT32是支持33/66MHz工作频率、32位PCI总线、支持主/从模式的PCI IP功能模块。考虑到市场的需求,通常的PC主板都支持32位PCI,且在主模式下DMA控制器才能工作,因此选择了PCI_MT32。 本地信号都以l (local)开头,其中以lt_开头的是从控信号,以lm_开头的是主控信号。

要使用PCI_MT32功能模块就要了解其配置寄存器,配置寄存器中的基址寄存器最为重要,PCI_MT32共提供了6个基址寄存器,可以映射6个存储器或I/O 空间。在操作系统启动前后,基址寄存器分别起到两个作用。在操作系统启动前,基址寄存器存放定义的空间长度。以使加电软件以确定在系统中有多少存储器以及系统中的 I/O 控制器要求多少地址空间,然后才可以把 I/O 控制器映射到合理的地址空间并引导系统。在操作系统启动后,基址寄存器又要起到存放基地址的作用,通过对要存取的基址寄存器用配置写操作写入基地址,再通过基地址加偏移量就可以访问想要存取的空间。

图2 FPGA控制电路内部框图

主控逻辑模块

当PCI_MT32作为PCI总线主设备进行主模式操作时,主控逻辑模块对PCI_MT32本地侧信号进行控制以执行PCI主模式写事务,将FIFO的数据传送给从设备。同时还为DMA引擎提供PCI总线所处的状态,如总线是否处于数据阶段,是否有从设备终止等。

模块的主要设计思路:当PCI总线仲裁器允许PCI_MT32成为总线主设备时,PCI_MT32功能模块在本地侧输出lm_adr_ackn信号,表明地址阶段开始,此时主控逻辑模块应在l_adi线提供PCI地址,并在l_cbeni线提供PCI命令。在接下来的数据阶段,如果本地侧数据已准备好,就使lm_rdyn(本地侧主设备准备好)信号有效,并在l_adi线提供数据,在l_cbeni线提供字节使能。如果从设备被选中且准备好,数据传输就开始了。最后,通过通知PCI总线当前周期是本地侧最后的数据阶段,在完成这次数据传输后就进入总线空闲状态,PCI_MT32不再是总线主设备,一次数据传输也就结束了。

从控逻辑模块

当PCI_MT32作为PCI总线从设备进行目标事务操作时,从控逻辑模块对PCI_MT32本地侧信号进行控制。PC通过读本地侧相应寄存器,了解当前状态,通过对相应DMA寄存器的写操作,来启动DMA引擎。由于对寄存器的读写只用到目标单周期事务,且大部分信号由主机控制,从控逻辑相对简单。主要是保证在要存取的目标地址命中,且frame信号有效时,trdyn(从设备准备好)信号有效。

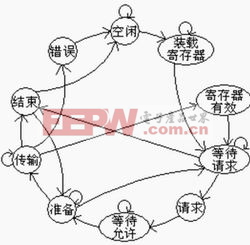

图3 DMA状态机流程图

评论