基于双FPGA+ARM架构的图像压缩系统

对于图像经过FPGA压缩后的码流,系统采用ARM芯片进行管理,该芯片为Cirrus Logic公司的工业级嵌入式处理器EP9315[8]。该处理器具有ARM920T核,最高主频达200 MHz,并具有丰富的外围接口,包括网络、USB、音频等。FPGA和ARM之间通信由I2C总线完成,当FPGA完成一帧图像压缩后,通过FPGA的GPIO发送一个终端信号给ARM,并准备好一帧码流长度等信息。ARM中断服务程序响应该中断,通过I2C接口读走码流长度,通过映射SRAM的方式从FPGA读取压缩码流到ARM内存,然后以文件的形式存储码流到本地硬盘,或者通过网络发送到远端服务器。

2 实验结果与性能

2.1 算法性能验证

系统设计初期,用软件对算法的性能进行了验证。在PC上对一组Lena等标准图像进行压缩,得到不同的重建图像,对重建图像求解PSNR值,式(2)为PSNR计算公式。其中Mean Square Error(MSE)表示原始图像和重建图像对应像素的均方误差值。

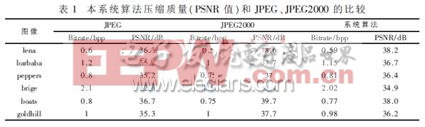

表1为本系统采用算法与JPEG及JPEG2000对标准图像压缩后重建图像的PSNR比较。从表中可以看出,本系统采用算法远优于JPEG,接近JPEG2000。PSNR值的比较以压缩比(对应表中Bitrate)为基准,即在相同压缩比的情况下对比PSNR值。

2.2 硬件实现和硬件压缩

硬件系统电路板采用10层板制作工艺,电路板面积为30.8 cm×16.7 cm,在100 MHz工作频率下对系统测试,结果表明系统工作稳定。表2为系统对1 600×1 200、1 280×1 024和1 024×768三种常见分辨率的计算机屏幕进行的记录,记录的图像源采用了各类计算机屏幕常见图像,如Word文档、PPT文件、动态雷达图像和一段视频。其中,PPT的平均翻页速度为60 s。由表2可以看出,系统对于Word文档、PPT文档等只有局部变化的图像能够达到非常高的压缩比,压缩帧率约为60帧/s。

本文结合应用提出图像压缩算,以FPGA为核心计算平台,设计了一套计算机屏幕图像记录系统。系统实现了对1 280×1 024×24 bit图像每秒记录27帧,对1 600×1 200×24 bit图像每秒记录17帧,对PPT、Word文档等只有局部变化的屏幕图像每秒可记录60帧,且压缩后重建图像质量优于JPEG,与JPEG2000接近。同时,对于压缩后的码流,系统采用ARM以文件的方式管理,有利于码流本地存储以及通过网络传输等灵活的应用。另外,系统支持多种输入接口,提高了硬件系统的灵活性,具有广阔的应用前景。

评论