联华电子与SuVolta 宣布联合开发28纳米低功耗工艺技术

联华电子公司(NYSE: UMC; TWSE: 2303) ("UMC") 与SuVolta公司,日前宣布联合开发28纳米工艺。该项工艺将SuVolta的Deeply Depleted Channel™ (DDC)晶体管技术集成到联华电子的28纳米High-K/Metal Gate(HKMG)高效能移动(HPM)工艺。SuVolta与联华电子正密切合作利用DDC晶体管技术的优势来降低泄漏功耗,并提高SRAM的低电压效能。

本文引用地址:http://www.eepw.com.cn/article/147840.htm这两家公司还宣布该工艺技术将提供高度灵活的采用方式:

· “DDC PowerShrink™低功耗平台”选项:所有晶体管都使用DDC技术以实现最佳功耗与效能优势;

· “DDC DesignBoost晶体管调换”选项:用DDC晶体管取代现有设计中部分晶体管。该选项的典型应用是用DDC晶体管取代泄漏功耗大的晶体管来降低泄漏,或者取代SRAM位单元晶体管从而提高效能并降低最低工作电压(Vmin)

联华电子先进技术开发部副总裁游萃蓉表示:“在接下来的几周或者几个月,我们期待看到联华电子与SuVolta联合开发的技术有良好的结果,从而进一步验证DDC技术为我们的28纳米 HKMG工艺带来的功耗与效能优势。通过将SuVolta的先进技术引进到我们的HKMG工艺上,联华电子将提供28纳米移动计算工艺平台,以完善我们现有的Poly-SiON及HKMG技术。”

SuVolta总裁兼首席执行官Bruce McWilliams博士表示:“联华电子与SuVolta团队继续将DDC技术集成到联华电子的28纳米工艺,取得优秀的进展。通过合作,我们开发的工艺使得联华电子客户的设计易于移植。此外,SuVolta为业界提供选择,以替代昂贵而复杂的工艺技术,从而推动未来移动器件的发展。”

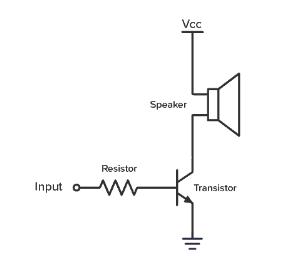

晶体管相关文章:晶体管工作原理

晶体管相关文章:晶体管原理

评论