基于MCU+FPGA的航空总线接口板测试平台设计

引言

本文引用地址:https://www.eepw.com.cn/article/123977.htm本文的项目背景是为了测试在航空领域CAN总线和高速异步总线的通信状况。CAN(控制器局域网)总线是由ISO(国际标准化组织)定义的有效支持分布式控制和实时控制的多组串行通信总线,由于其在通信能力、实时性、灵活性、易用性、传输距离远、可靠性等方面有着明显的优势,日益受到人们的重视,在航空等领域已得到广泛应用,成为目前比较流行的现场总线之一。RS485标准的全称为TIA/EIA-485串行通讯标准,为弥补RS-232通信距离短、速率低等缺点而产生的,其数据采用平衡发送和差分接收,具有抑制共模干扰的能力,抗噪声干扰性好。RS485具有多站能力(在总线上允许连接多达128个收发器),是一种相对经济、具有相当高噪声抑制、相对高的传输速率、传输距离远的半双工异步总线。LVDS(低压差分信号传输)具有小摆幅差分特性使其成为一种高速低噪声、高噪声抑制能力、较低的电磁干扰、低功率技术,保证了可靠的信号传输,能满足当今高性能数据传输应用的新型技术。此技术基于ANSI/TIA/EIA-644LVDS接口标准。

功能介绍

本测试平台采用FPGA+MCU为基本运行平台,通过CAN总线、高速异步总线进行数字信号的传输,主要用作对接口板功能的完整性、正确性进行测试分析。通过RS232接口连接到上位机实现数据的实时发送和接收,以及对CAN总线和高速异步总线的波特率等参数实施动态控制。

硬件电路设计

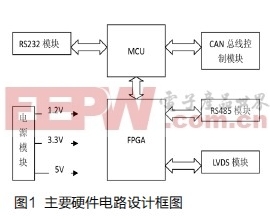

本测试平台对CAN数据传送采用了双冗余备份总线,支持8路高速异步总线同时传送数据,其中4路为RS485电平,4路为LVDS电平。主要由MCU(微控制器)控制模块、FPGA(现场可编程逻辑阵列)模块、CAN总线控制模块、RS485接口模块、LVDS接口模块、RS232模块以及电源模块组成。主要硬件电路设计框图如图1。

Atmel公司的MCU器件选用Atmel公司的ATmega128-16AI,时钟频率11.0592MHz。ATmega128为基于AVR RISC结构的8位低功耗CMOS微处理器。由于其先进的指令集以及单周期指令执行时间,ATmega128 的数据吞吐率高达1MIPS/MHz,从而可以缓减系统在功耗和处理速度之间的矛盾。MCU是整个总线控制器的核心,主要实现CAN总线信号的处理、与上位机通信以及对FPGA和上位机通信进行中转。FPGA选用Xilinx公司XC3SD3400A-4CS484,时钟频率50MHz,主要实现高速异步总线的处理、接收MCU的控制指令与MCU进行数据交互。

评论