SDRAM接口时序和PCB布线长度的分析

引言

本文引用地址:https://www.eepw.com.cn/article/123975.htm经常看到有文章介绍对SDRAM布线的各种要求,这只是工程上的经验总结,不同的芯片对时序的要求不同,对走线也有不同的要求,不能一概而论。其实,等长不是目的,真正的目的是满足芯片的建立保持时间,采样正确。由于FR4中的走线的传播延时近似值为6英寸/ns,根据时序关系可以转化为PCB Layout(印制板布局)的走线线长关系。

因为触发器内部数据的形成是需要一定的时间的,如果不满足建立和保持时间,触发器将进入亚稳态,进入亚稳态后触发器的输出将不稳定,在0和1之间变化,这时需要经过一个恢复时间,其输出才能稳定,但稳定后的值还不一定是你的输入值。所以为了保证接口数据传输正确,必须满足其建立保持时间。

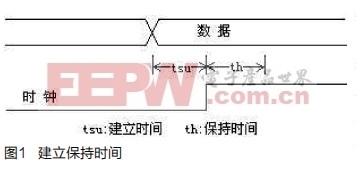

建立时间:触发器在时钟沿来到前,其数据输入端的数据必须保持不变的时间。

保持时间:触发器在时钟沿来到后,其数据输入端的数据必须保持不变的时间。见图1。

其实触发器的建立时间和保持时间比较短,为什么在接口的建立时间和保持时间却较长呢?因为总线的影响,造成封装和Die(芯片)中不同数据线传播延时不同,需要满足最快和最慢的数据线。另外时钟信号在输入芯片后,需要经过时钟树再传到接口触发器,造成时钟的延迟可能比数据线更慢。这两个原因造成接口信号的建立时间和保持时间需要有较多的冗余。我们研究接口的建立时间和保持时间,不需要关注芯片内部的延迟情况。

下面以SDRAM和DSP为例,说明SDRAM时序和PCB走线长度的关系。DSP为BF561,SDRAM为H57V2562GFR。SDRAM工作在133MHz,CL=3。

SDRAM和DSP接口时序分析

控制信号(单向)

建立时间应满足:

tosu(DSP) + tClockRouteDelay – tControlRouteDelay(Slowest) ≥ t isu(SDRAM)

即:tControlRouteDelay(Slowest) – tClockRouteDelay ≤ tosu(DSP) – tisu(SDRAM)

评论