实时上市加成本优势 SiP在高整合芯片技术脱颖而出

2010年最受终端市场瞩目的热门电子产品,就非Apple所推出iPad的Tablet PC莫属。iPad尺寸规格为长24.5公分、宽19公分、高1.3公分,重量则仅介于0.68~0.73公斤间,与一般笔记型计算机(NB)规格相较,长宽高大约分别为26公分、37.5公分、3公分,重量则约达2.5公斤,无论是体积或重量,iPad皆较NB易于携带。

本文引用地址:https://www.eepw.com.cn/article/113354.htmiPad之所以能达到短小轻薄的设计要求,除采用LED背光与投射式电容多指触控等技术外,半导体组件高度整合亦是重要因素之一。

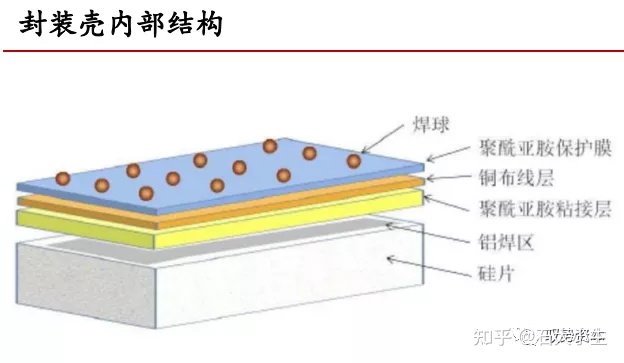

从 iPad所采用新型A4微处理器纵剖面观察,主要由3层芯片堆栈而成,最上面2层为三星电子(Samsung Electronics)1Gb的Mobile RAM,显示内含2Gb内存,相当于每颗晶粒的内存容量为128MB,合计为256MB。

第3层则为A4微处理器的裸晶,3层芯片则以系统级封装(System in Package)技术之一的层迭封装(Package on Package;PoP)技术封装于同一颗IC之中。

实际上,不止是iPad,包括iPhone在内的智能型手机、高容量记忆卡与储存装置、数字相机(DSC)与可携式多媒体播放器等消费性电子产品,早已采用SiP技术整合与封装内部半导体组件,而且采用SiP的渗透率与单位使用颗数都将持续增加。

另一方面,在制程持续微缩的同时,不止让SoC的设计时间与设计难度提升,投片前的前置费用更是倍数成长,成本竞争优势持续丧失中,更将有利于SiP为终端电子产品市场所接受。

评论