TPACK与Cypress联手为以太网交换和流量管理提供参考设计

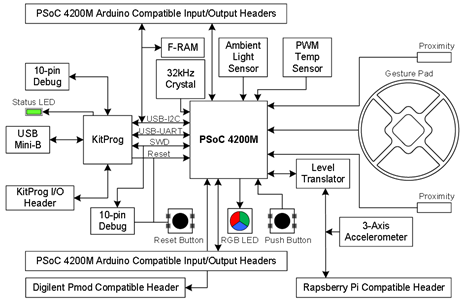

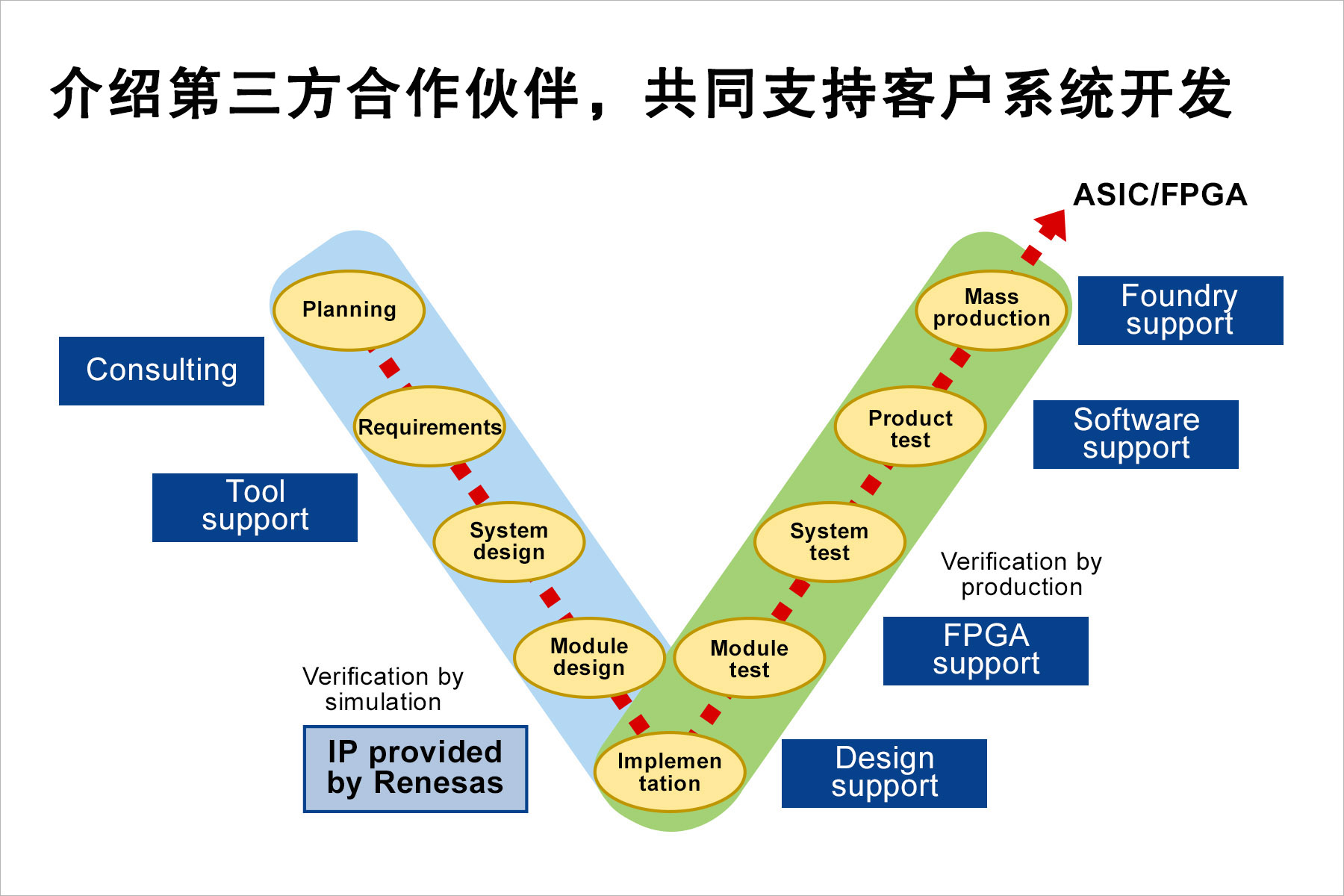

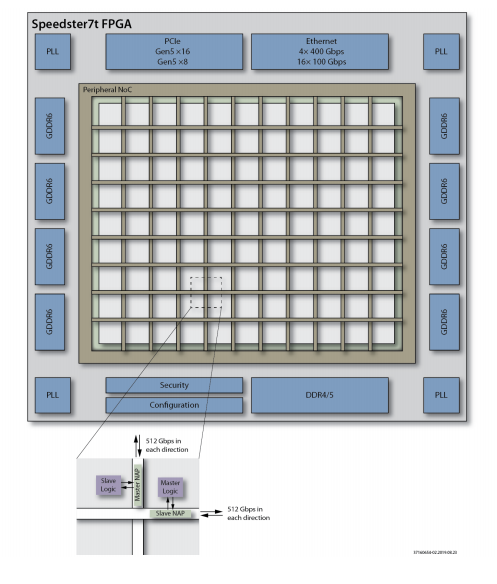

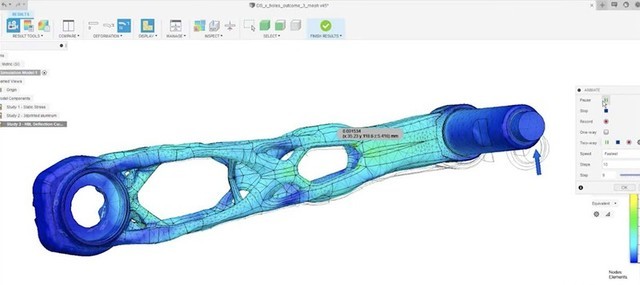

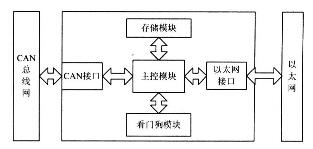

SRAM行业的领导者赛普拉斯,与领先的核心数据传输及交换功能IC的供应商TPACK日前联合宣布,为超高速以太网交换和排队管理应用推出一款参考设计。全新的Springbank参考设计结合了TPACK的 TPX4004高容量集成包处理器和流量管理器,以及赛普拉斯的CY7C15632KV18 72-Mbit Quad Data Rate™II+ (QDR™II+)SRAM,从而能提供最快的速度,并且未来升级非常简单。TPACK参考设计还提供对各类FPGA的便捷接口,拥有强大的应用支持。

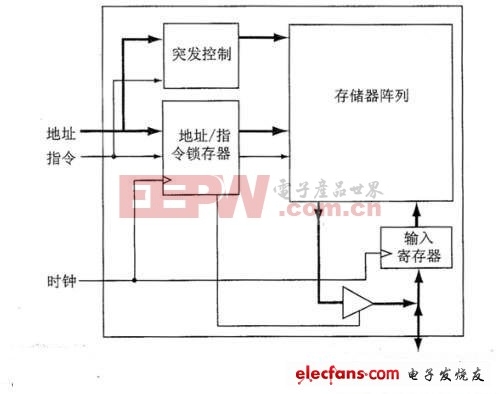

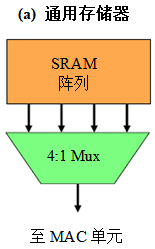

本文引用地址:https://www.eepw.com.cn/article/107368.htmTPACK的高可靠性40-Gbps TPX4004提供真正的城域以太网论坛(MEF)定义的运营商级别的性能。其超级灵活、功能丰富的第二层解决方案具有适应不同系统架构和要求的能力。赛普拉斯的QDRII+是业界首款量产的65-nm线宽SRAM。赛普拉斯的SRAM通过一个36-bit I/O的QDRII+器件,可以实现业界最快的高达550 MHz的时钟速度以及80 Gbps的总数据率,而功耗只有90-nm SRAM的一半。

TPACK 产品线管理副总裁Thomas Rasmussen说:“能够首先推出这款参考设计,显示了我们在用于运营商以太网交换和流量管理的高数据吞吐率外部存储器解决方案领域的技术领导地位。与赛普拉斯这样的SRAM领导者合作,保证了我们产品的最高性能和可靠性。”

赛普拉斯同步存储器和时序产品副总裁David Kranzler说:“TPACK的高性能Springbank参考设计是个非常出色的平台,能够充分展示我们65-nm QDRII+ SRAM在网络市场的先进设计中所具有的惊人速度。我们期待在未来的项目上与TPACK就SRAM和我们强大的用于网络的时序解决方案产品线继续合作。”

与其90-nm前辈相比,赛普拉斯的65-nm QDR 和 DDR SRAM将输入和输出电容减少了60%。QDRII+ 和 DDRII+器件具有片内终结器(ODT),因为不需要外部中断电阻,所以能改善信号的完整性,降低系统成本并节约板级空间。65-nm器件采用了先进设计和技术,使得数据有效窗口拓宽了35%,从而为客户节省了研发时间和成本。

评论