- 十多年前,半导体设计与应用工程师在有了可行 CMOS 硅芯片时高兴得相互击掌庆祝,因为它可在 80% 的良率下实现 100uV 以下的放大器输入失调电压。当时,Allen Bradley、John Deere、Rockwell Automation 以及 Siemens 等工业领域巨头都考虑将 CMOS 放大器作为较低成本的平台,但它们很少将其用于实现高性能。

尽管双极性技术依然盛行,但新型 CMOS 放大器正在以先进的设计技巧、高级的微调方法以及提高的良率逐渐打破工艺局限性。

以往,双极

- 关键字:

CMOS 放大器

- IC通路商大联大积极扩大物联网、工业及车用市场布局,旗下世平近日再新增代理无线射频晶片厂RFaxis的主要产品线CMOS RFeIC;由于RFaxis已获联发科、展讯公板设计的协力厂商,为大联大在亚太市场布局物联网增添实力。

RFaxis指出,物联网感测器节点的单价,应该低于1美元才有可能获得大规模普及,这意味着传统的GaAs(砷化镓)或SiGe(矽锗)无线射频晶片,几乎难有任何利润的空间,而RFaxis所推出的纯CMOS的裸片解决方案,不论在封装规格、性能与成本等各方面,更符合其价格需求。

- 关键字:

大联大 物联网 CMOS

- 韩系半导体大厂SK海力士(SK Hynix)为量产CMOS影像传感器(CIS),将引进研究用途系统芯片(SoC)用12吋晶圆蒸镀设备,吸引业界关注。CIS为智能型手机相机模块、医学用摄影设备等IT、数字装置广泛使用的非内存芯片,近来使用范围也扩大到车用半导体。

据南韩MT News报导,SK海力士近来向南韩一半导体设备制造厂采购非内存用分区化学气相沉积(Space Divided Plasma CVD;SDPCVD)设备。该设备将设置在SK海力士利川工厂研究园区中,进行CIS研究开发。

S

- 关键字:

海力士 CMOS CIS

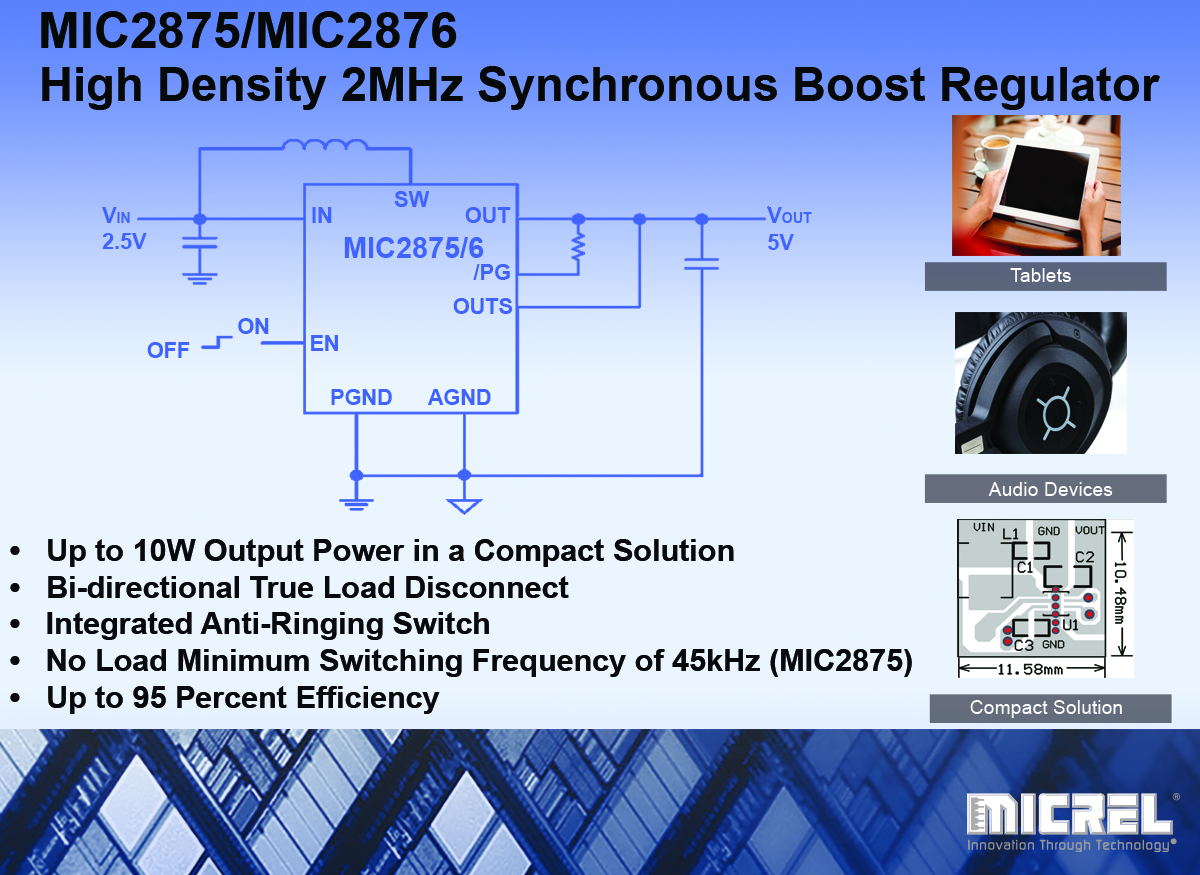

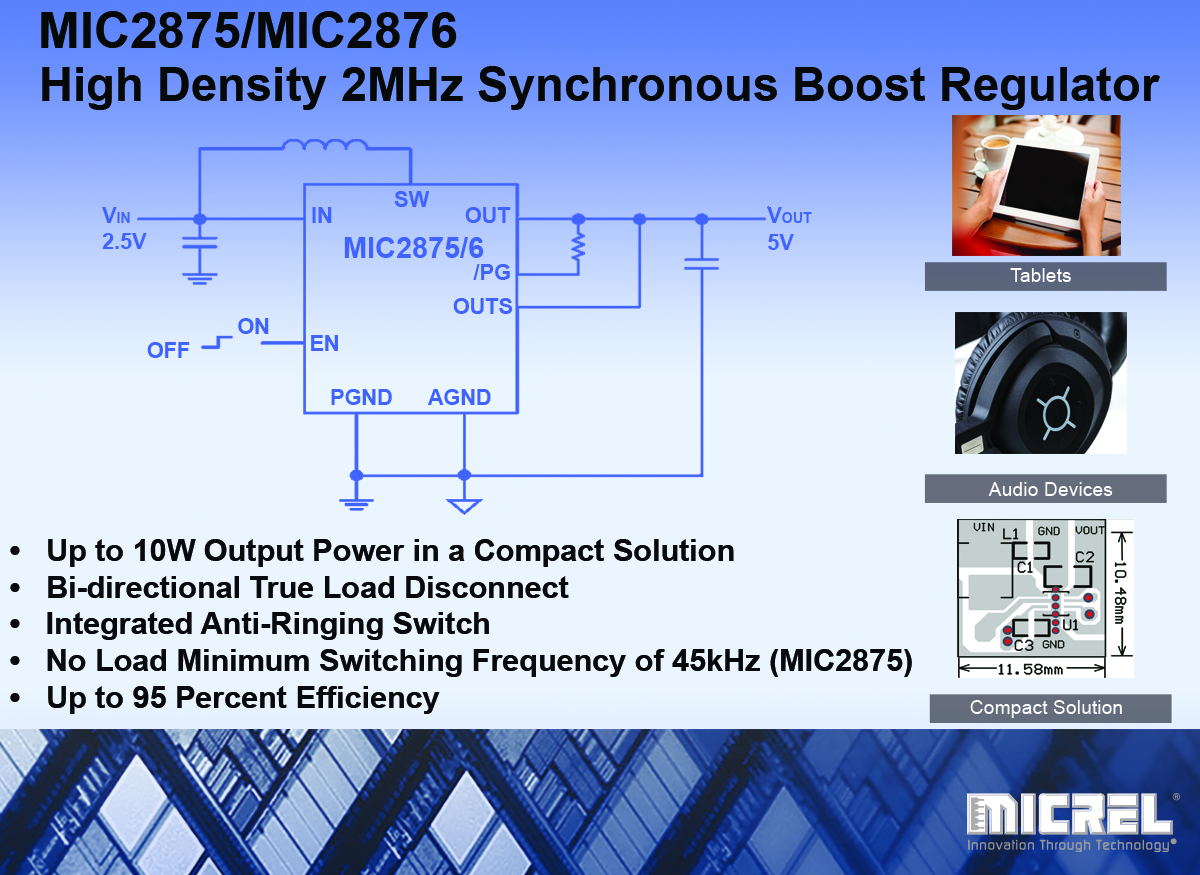

- 高性能线性和电源解决方案、局域网以及时钟管理和通信解决方案领域的行业领导者麦瑞半导体公司 (Micrel, Inc.) 和先进的光学与微机械传感器系统制造商 Silicon Micro Systems (SMS) 今天发布用于汽车和工业系统的全新 HDR-CMOS 百万像素以太网摄像头。这款可投入生产的摄像头由摄像头专家 SMS(First Sensor 子公司 Silicon Micro Sensors GmbH)设计和制造,采用了麦瑞半导体独特的低放射网络解决方案。

First

- 关键字:

麦瑞半导体 Silicon Micro Sensors HDR-CMOS

- 台积电昨(12)日宣布,完成16纳米主流制程FinFET+(鳍式场效晶体管强化版)全球首颗网通芯片及手机应用处理器试产,预定本月完成所有可靠性试验,明年7月正式量产。

这是台积电拓展先进制程一大里程碑。业界认为,正值三星再度与台积电争夺苹果下世代A9处理器订单之际,台积电16纳米FinFET+技术到位后,将进一步拉大与三星差距,对台积电而言,A9订单「有如探囊取物」,最快明年夏天开始投产A9芯片。

台积电昨天不对单一客户导入16纳米制程状况置评,强调明年底前,估计将完成近60件产品设计定案

- 关键字:

台积电 FinFET+

- 是德科技公司日前宣布赞助台湾大学(NTU)高速射频与毫米波技术中心的 B4G MIMO 实验室。是德科技同时参加了揭牌仪式后举行的 B4G/5G 技术论坛。B4G MIMO 实验室是台湾大学高速射频与毫米波技术中心实施的项目之一,旨在开发未来 4G 和 5G 移动通信系统的关键元器件。

5G 正在逐步成为满足移动互联网使用需求的核心技术,为此台湾当局主管部门鼓励学术界开发未来技术,并号召台湾大学这所知名学府:1. 建立高速射频和毫米波技术中心,2. 研究先进技术,3. 进一步推动当地产业发展。是

- 关键字:

是德科技 B4G CMOS

- 中国大陆并不以台湾为假想敌,但是,国内的实力是实实在在的,无论从制程、还是手机芯片方面,台湾都感受到了压力......

- 关键字:

半导体 集成电路 CMOS

- 行动装置如智慧型手机、平板电脑等应用领域,对于半导体晶片的需求走到超低功耗,制程技术从28奈米制程,到20奈米制程,将于2015年进入第一代3D设计架构的FinFET制程,也就是14/16奈米世代。

台积电2015年下半即将量产16奈米世代,英特尔、三星电子(Samsung Electronics)、GlobalFoundries将是14奈米制程世代,英特尔早一些量产,之后是三星,GlobalFoundries制程技术将属于三星阵营。

台积电因为为大客户苹果生产20奈米制程晶片,因此16奈

- 关键字:

16纳米 FinFET

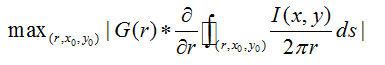

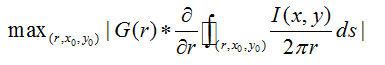

- 7.1.3 虹膜外边缘的确定

(1) 虹膜外边缘的特征分析

由图1中所示的虹膜图像可以看出,虹膜外边缘的主要特点是:较相对与虹膜内边缘而言,边缘处灰度变化不是特别明显,有一小段渐变的区域。也就是说,虹膜内部灰度趋近于一致这个事实,在参考文献[8]中,介绍的环量积分算子应该式是一种有效的方法。

即:

(7-10)

(2) 采用环量积分算子实现虹膜外边缘的检测

如上分析,虹膜环量积分算子是检测虹膜外边缘的一种有效手段,为了克服虹膜纹理对环量线

- 关键字:

FPGA 虹膜识别 CMOS

- 项目信息

1.项目名称:基于FPGA的混沌加密虹膜识别系统设计

2.应用领域:工业控制、科研、医疗、安检

3.设计摘要:

基于虹膜的生物识别技术是一种最新的识别技术,通过一定的虹膜识别算法,可以达到十分优异的准确性。随着虹膜识别技术的发展,它的应用领域越来越宽,不仅在高度机密场所应用,并逐步推广到机场、银行、金融、公安、出入境口岸、安全、网络、电子商务等场合。在研究了虹膜识别算法,即预处理、特征提取和匹配的基础上,我们设计了一种可便携使用的基于FPGA的嵌入式虹膜识别系统。本系

- 关键字:

FPGA 虹膜识别 CMOS

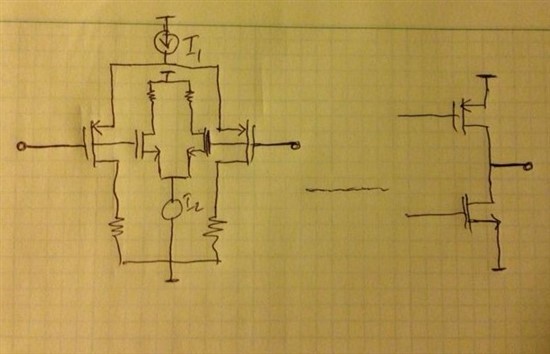

- 1 引 言

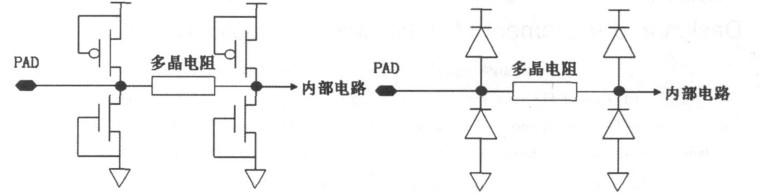

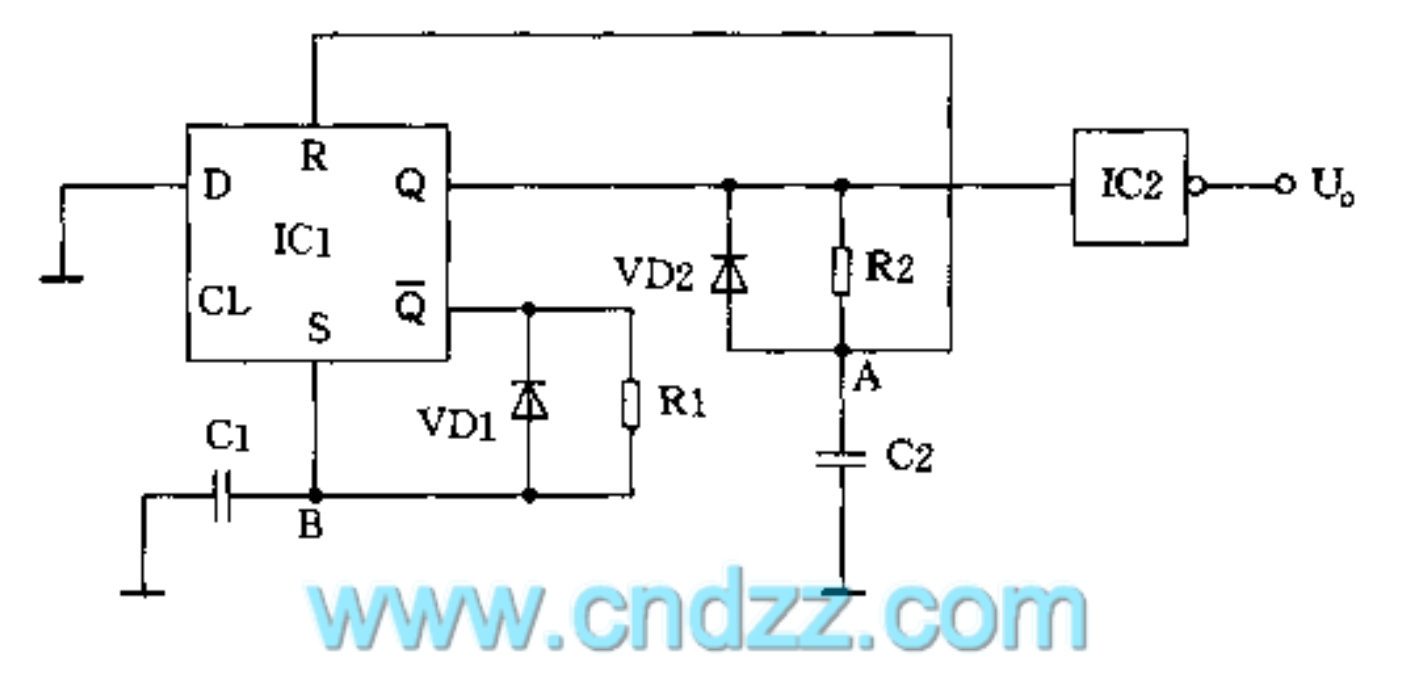

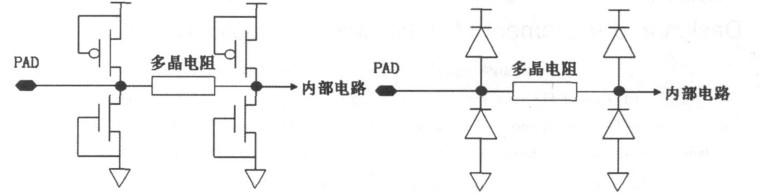

静电放电会给电子器件带来破坏性的后果,它是造成集成电路失效的主要原因之一。随着集成电路工艺不断发展, CMOS电路的特征尺寸不断缩小,管子的栅氧厚度越来越薄,芯片的面积规模越来越大,MOS管能承受的电流和电压也越来越小,而外围的使用环境并未改变,因此要进一步优化电路的抗ESD性能,如何使全芯片有效面积尽可能小、ESD性能可靠性满足要求且不需要增加额外的工艺步骤成为IC设计者主要考虑的问题。

2 ESD保护原理

ESD保护电路的设计目的就是要避免工作电路成为ESD的放电通路

- 关键字:

CMOS ESD MOS

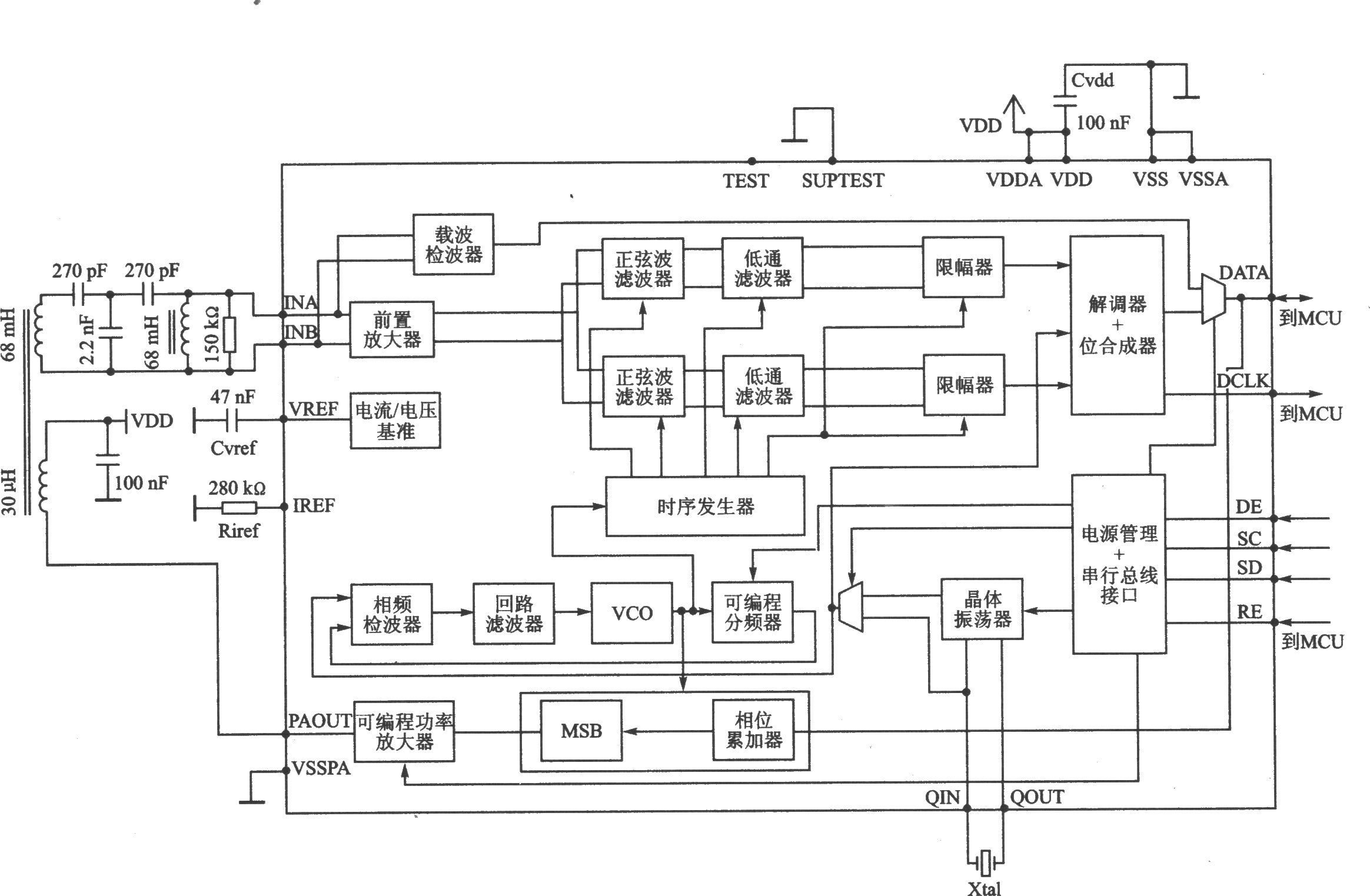

- 1引言

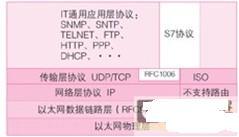

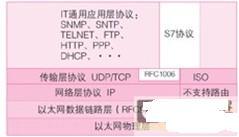

在当今自动化领域,网络结构已经被广泛地应用于各行各业的工业环境中,它是构成各类控制系统的基础,其性能直接影响着系统整体的综合指标,不同的网络种类形式如:串口通讯、现场总线、以太网等已在各类场合获得了验证和发展,但随着近年来it技术的迅猛发展,这种格局正在发生着巨大的变化,特别是以太网技术正由商业向工业、上层向低层、低速向高速、非实时向实时、封闭向透明、层次化向扁平化等方面全面发展和延伸,并融合了各类现场总线的技术和协议,再加上低成本的刺激和速度的提高因素,全球各自动化巨头厂商也不断推出&

- 关键字:

西门子 以太网 cmos

- “合抱之木,生于毫末;九层之台,起于垒土;千里之行,始于足下。” 老子《道德经》

对于新手来说,如何上手调试FPGA是关键的一步。

对于每一个新设计的FPGA板卡,也需要从零开始调试。

那么如何开始调试?

下面介绍一种简易的调试方法。

(1) 至少设定一个输入时钟 input sys_clk;

(2) 设定输出 output [N-1:0] led;

(3)设定32位计数器 reg [31:0] led_cnt;

(4) 时钟驱动

- 关键字:

FPGA JTAG CMOS

- 日前,德州仪器(TI)宣布其内部组装点的铜线键合技术产品出货量已超过220亿件,目前正在为汽车和工业等高可靠性应用进行批量生产。TI现有的模拟和CMOS硅芯片技术节点大多数已用铜线标准来限定,且所有新技术和封装都在用铜线键合法来开发。铜线能提供与金线同等或更佳的可制造性,同时还具有可靠的质量并可节约成本。此外,铜线还能提供比金线高40%的导电性,从而可以用TI的多种模拟和嵌入式处理部件提升用户的整体产品性能。

“TI已率先开发出铜线键合法,该产品可适用于广泛的产品和技术中,并可在多家

- 关键字:

德州仪器 CMOS TSSOP

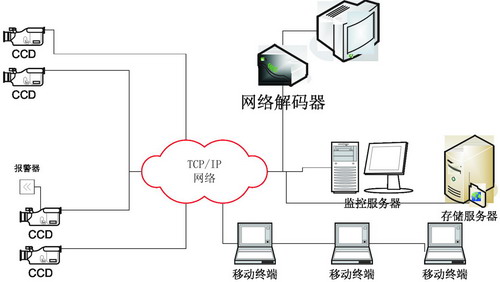

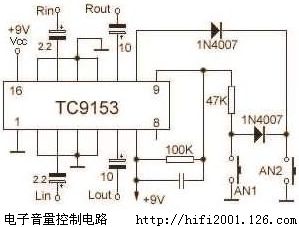

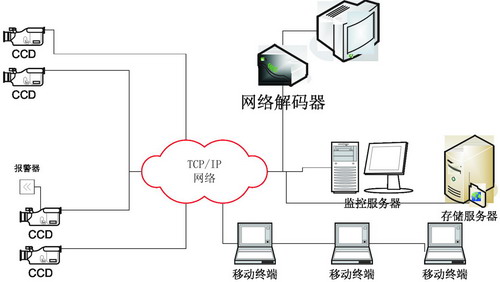

- 网络摄像机是传统摄像机与网络视频技术相结合的新一代产品,除了具备一般传统摄像机所有的图像捕捉功能外,机内还内置了数字化压缩控制器和基于WEB的操作系统,使得视频数据经压缩加密后,通过局域网,Internet或无线网络送至终端用户。网络摄像机的应用,使得图像监控技术有了一个质的飞跃。第一,网络的综合布线代替了传统的视频模拟布线,实现了真正的三网(音频、视频、数据)合一,网络摄像机即插即用,工程实施简便,系统扩充方便;第二,跨区域远程监控成为可能,特别是利用互联网,图像监控已经没有距离限制,而且图像清晰,

- 关键字:

网络摄像机 CMOS CCD

cmos finfet介绍

您好,目前还没有人创建词条cmos finfet!

欢迎您创建该词条,阐述对cmos finfet的理解,并与今后在此搜索cmos finfet的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473