- 据外媒EENews消息,美国Cadence公司并购了总部位于英国布里斯托尔(Bristol)的Pulsic半导体设计公司。报道称,一位发言人证实交易已经完成,并表示将在未来几周内提供更多细节。据悉,Pulsic于2000年由来自Zuken的工程师组成,他们在布里斯托尔也有一个工具设计中心。资料显示,Cadence成立于1988年,由ECAD Systems和SDA

Systems两个公司合并而成,目前已成为全球EDA龙头企业之一。Pulsic亦是一家拥有20多年历史的EDA软件公司,已为全球存储、FP

- 关键字:

Cadence Pulsic

- 3nm 时代来临了!Cadence 在 2023 年 TSMC 北美技术研讨会期间发布了面向台积电 3nm 工艺(N3E)的 112G 超长距离(112G-ELR)SerDes IP 展示,这是 Cadence 112G-ELR SerDes IP 系列产品的新成员。在后摩尔时代的趋势下,FinFET 晶体管的体积在 TSMC 3nm 工艺下进一步缩小,进一步采用系统级封装设计(SiP)。通过结合工艺技术的优势与 Cadence 业界领先的数字信号处理(DSP)SerDes 架构,全新的 112G-ELR

- 关键字:

Cadence TSMC 3nm工艺 SerDes IP

- · 这是一个业界用于打造差异化定制芯片的领先平台,可借助生成式 AI 技术显著提升设计生产力;· Virtuoso Studio 与 Cadence 最前沿的技术和最新的底层架构集成,助力设计工程师在半导体和 3D-IC 设计方面取得新突破;· 依托 30 年来在全线工艺技术方面取得的行业领先

- 关键字:

Cadence Virtuoso Studio

- 新加入的生态系统成员包括 Kudan 和 Visionary.ai,有助于快速部署高性能、高能效的基于 SLAM 和 AI ISP 的解决方案 中国上海,2023 年 4 月 12 日 —— 楷登电子(美国 Cadence 公司,NASDAQ:CDNS)今日宣布欢迎 Kudan 和 Visionary.ai 加入 Tensilica 软件合作伙伴生态系统,他们将为 Cadence® Tensilica® Vision DSP 和 AI 平台带来业界领先的同步与地图构建 (SLAM)和 AI 图像

- 关键字:

Cadence Tensilica Vision AI 软件

- 中国上海,2023 年 4 月 7 日 —— 楷登电子(美国 Cadence 公司,NASDAQ:CDNS)今日宣布推出 Cadence® Allegro® X AI technology,这是 Cadence 新一代系统设计技术,在性能和自动化方面实现了革命性的提升。这款 AI 新产品依托于 Allegro X Design Platform 平台,可显著节省 PCB 设计时间,与手动设计电路板相比,在不牺牲甚至有可能提高质量的前提下,将布局布线(P&R)任务用时从数天缩短至几分钟。

- 关键字:

Cadence Allegro PCB

- 半导体行业在了解 IC 老化如何影响可靠性方面正在取得进展,但仍有问题待解决。

- 关键字:

Cadence 仿真

- 内容提要:· Cadence 凭借关键的 EDA、云和 IP 创新荣获 TSMC 大奖;· Cadence 是 TSMC 3DFabric 联盟的创始成员之一。 中国上海,2022年12月14日——楷登电子(美国 Cadence 公司,NASDAQ:CDNS)今日宣布,其 EDA、IP 和云计算解决方案获得了 TSMC 颁发的六项 Open Innova

- 关键字:

Cadence 2022 TSMC OIP

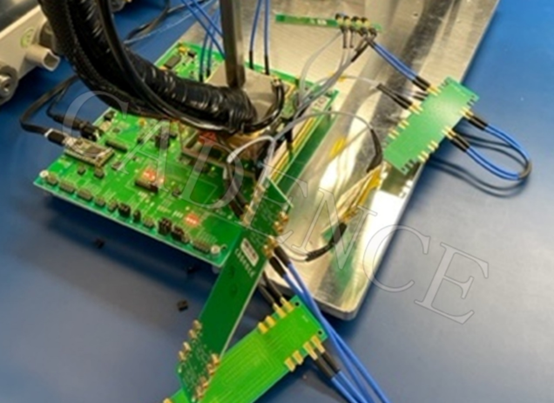

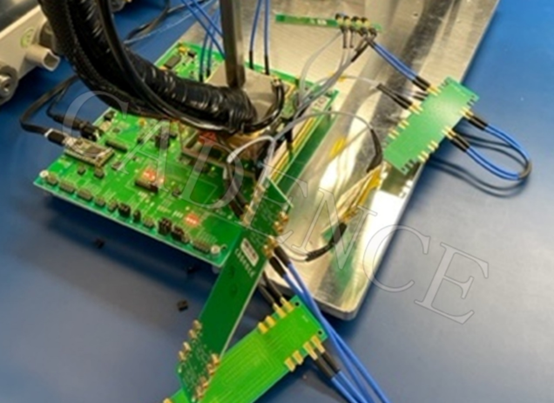

- 联华电子与全球电子设计创新领导厂商益华计算机(Cadence Design Systems, Inc.)于今(30)日宣布双方合作经认证的毫米波参考流程,成功协助亚洲射频IP设计的领导厂商聚睿电子(Gear Radio Electronics),在联电28HPC+ 制程技术以及Cadence® 射频(RF)解决方案的架构下,达成低噪音放大器 (LNA) IC一次完成硅晶设计(first-pass silicon success) 的非凡成果。 经验证的联电28HPC+解决方案非常适合生产应用于高

- 关键字:

联电 Cadence 毫米波参考流程

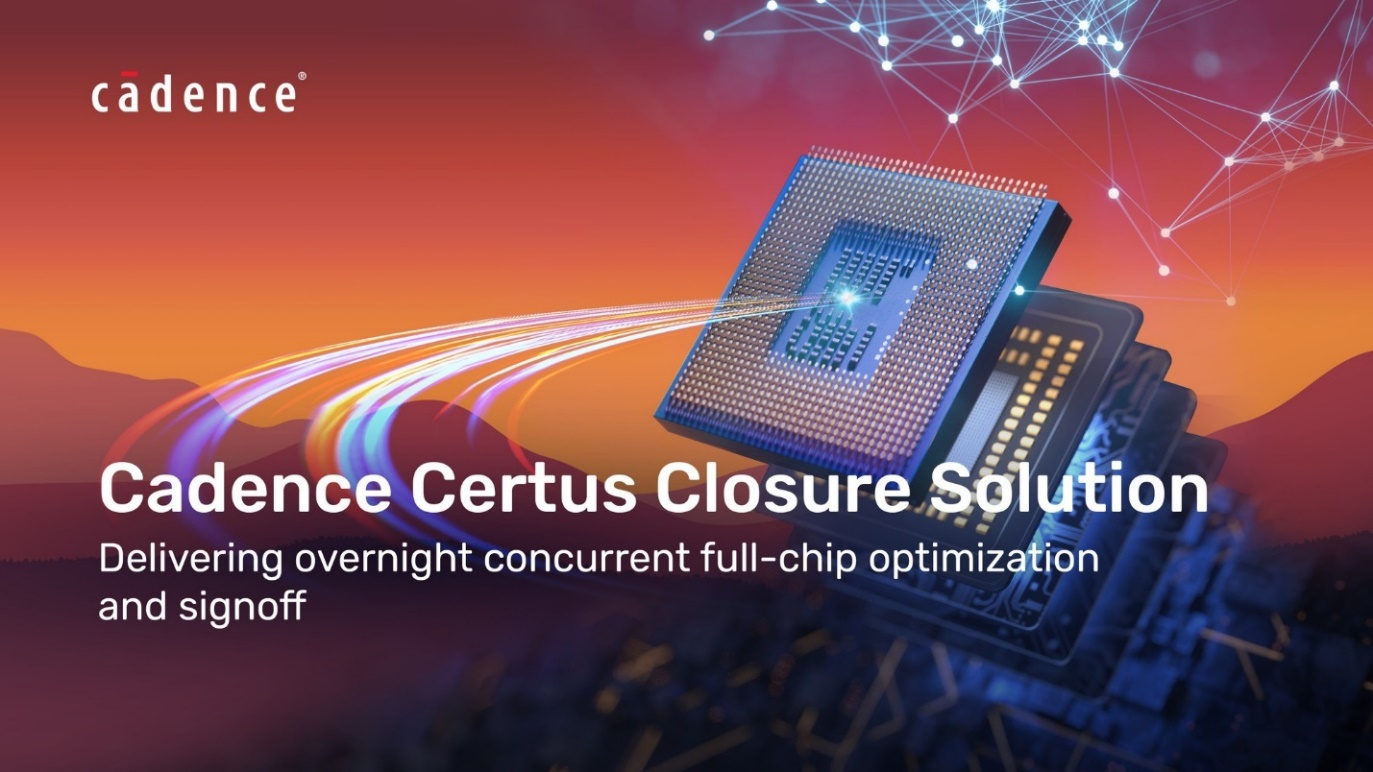

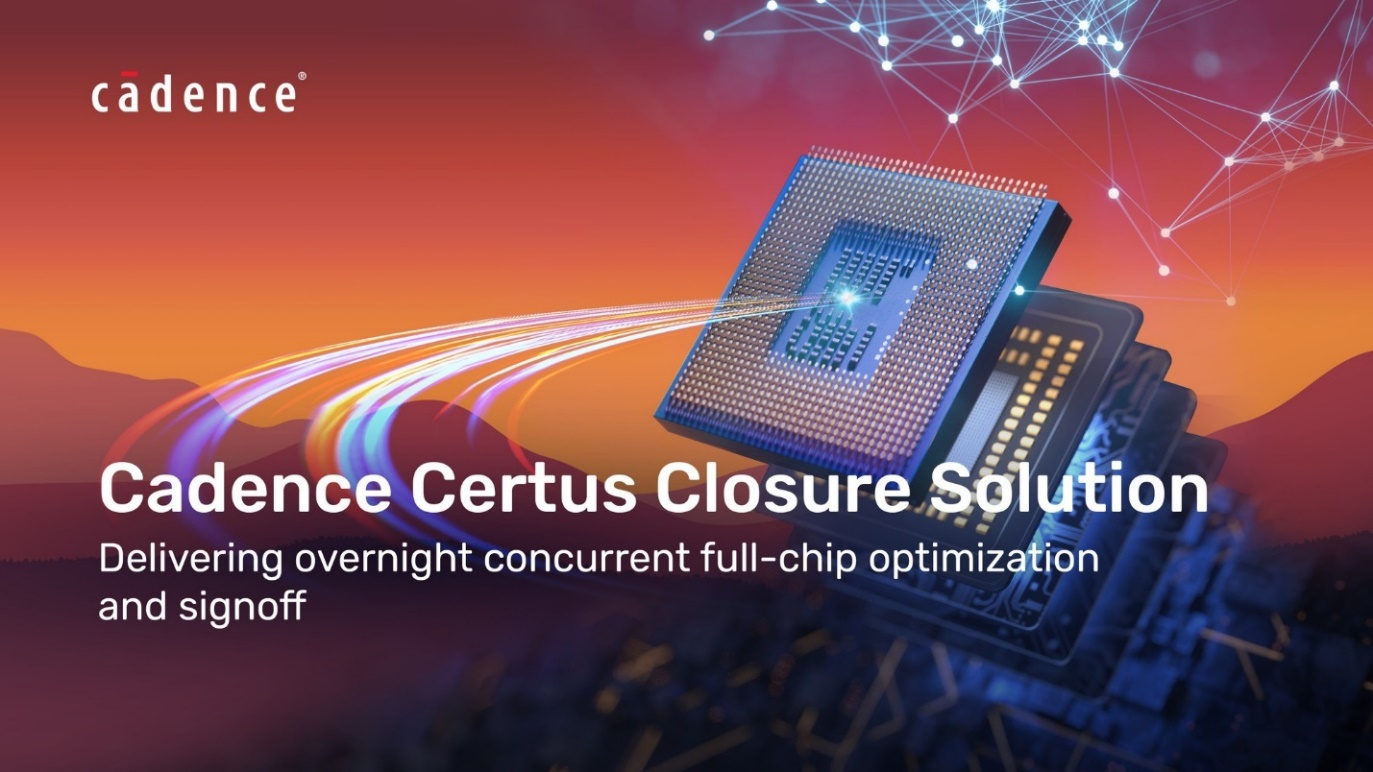

- 内容提要:● 为客户提供业内首个具有大规模并行和分布式架构的完全自动化环境;● 支持无限容量的设计优化和签核,周转时间缩短至一夜,同时大幅降低设计功耗;● 支持云的解决方案,推动新兴设计领域的发展,包括超大规模计算、5G 通信、移动、汽车和网络。楷登电子(美国 Cadence 公司)近日宣布推出新的 Cadence® Certus™ Closure Solution,以应对不断增长的芯片级设计尺寸和复杂性挑战。Ca

- 关键字:

Cadence 并行优化 签核速度

- 楷登电子(美国 Cadence 公司)近日宣布,推出 Cadence® Verisium™ Artificial Intelligence (AI)-Driven Verification Platform,整套应用通过大数据和 JedAI Platform 来优化验证负荷、提高覆盖率并加速 bug 溯源。Verisium 平台基于新的 Cadence Joint Enterprise Data AI (JedAI) Platform,并与 Cadence 验证引擎原生集成。随着 SoC 复杂性不断提高,

- 关键字:

Cadence Verisium AI-Driven Verification Platform 验证

- 联华电子与Cadence于今(8月24)日共同宣布,Cadence的模拟与混合信号(Analog/Mixed Signal, AMS)芯片设计流程获得联华电子22纳米超低功耗 (22ULP)与22纳米超低漏电(22ULL)制程认证,此流程可优化制程效率、缩短设计时间,加速5G、物联网和显示等应用设计开发,满足日渐增高的市场需求。 联电的22纳米制程具有超低功耗和超低漏电的技术优势,可满足在科技创新发展下,使用时间长、体积小、运算强的应用需求。经联电认证的Cadence AMS设计流程,提供了整合

- 关键字:

联电 Cadence 22纳米 模拟与混合信号

- 楷登电子(美国 Cadence 公司)今日宣布,其面向 TSMC N7、N6 和 N5 工艺技术 PCI Express®(PCIe®)5.0 规范的 PHY 和控制器 IP 在 4 月举行的业界首次 PCIe 5.0 规范合规认证活动中通过了 PCI-SIG® 的认证测试。Cadence® 解决方案经过充分测试,符合 PCIe 5.0 技术的 32GT/s 全速要求。该合规计划为设计者提供测试程序,用以评估系统级芯片(SoC)设计的 PCIe 5.0 接口是否会按预期运行。 面向 PCIe 5

- 关键字:

Cadence TSMC PCIe 5.0

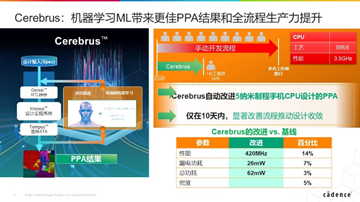

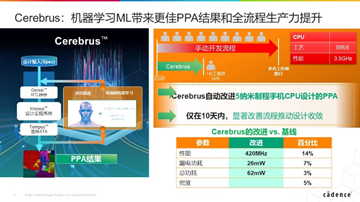

- Cadence Design Systems, Inc.宣布,Cadence CerebrusÔ智能芯片设计工具(Intelligent Chip Explorer) 获得客户采用于其全新量产计划。此基于 Cadence Cerebrus 采用人工智能 (AI) 技术带来自动化和扩展数字芯片设计能力,能为客户优化功耗、效能和面积 (PPA),以及提高工程生产力。Cadence Cerebrus 运用革命性的AI技术,拥有独特的强化学习引擎,可自动优化软件工具和芯片设计选项,提供更好的 PPA进而大幅减少工

- 关键字:

联发科 瑞萨 Cadence Cerebrus AI 芯片PPA

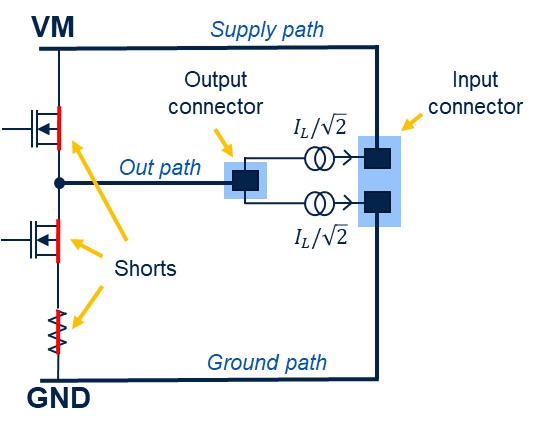

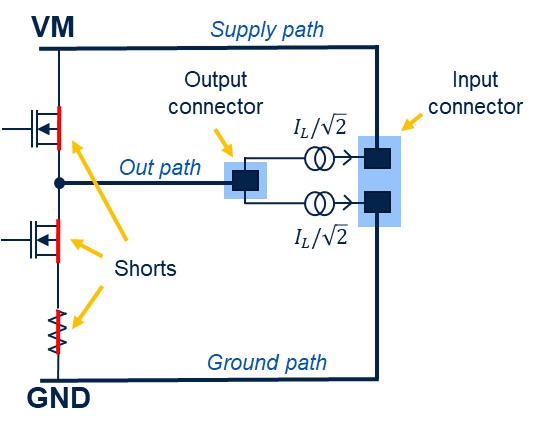

- 电池供电马达控制方案为设计人员带来多项挑战,例如,优化印刷电路板热效能至今仍十分棘手且耗时;但现在,应用设计人员可利用现代化电热仿真器轻松缩短上市时间。如今,电池供电马达驱动解决方案通常可用极低的工作电压提供数百瓦的功率。在此类应用中,为确保整个系统的效能和可靠性,必须正确管理马达驱动设备的电流。事实上,马达电流可能会超过数十安培,导致变流器内部耗散功率提升。为变流器组件施加较高的功率将会导致运作温度升高,效能下降,如果超过最额定功率,甚至会突然停止运作。优化热效能同时缩小大小,是变流器设计过程中的重要一

- 关键字:

电池供电 热感知 高功率高压板 ST Cadence

- 随着算力的不断提升,人工智能的应用逐渐渗透到各个行业。作为人工智能芯片最关键的开发工具EDA,是否也会得到人工智能应用的助力从而更好地提升服务效率呢?答案自然是肯定的。随着半导体芯片设计的复杂度不断提升,以及芯片包含功能的日渐广泛,EDA的设计过程越来越需要借助人工智能来尽可能避免一些常见的设计误区,并借助大数据的优势来实现局部电路设计的最优化。在可以预见的未来,随着人工智能技术的不断引入,借助大数据和机器学习的优势,EDA软件将可以提供更高效更强大的设计辅助功能。 近日,楷登电子(Cadenc

- 关键字:

人工智能 EDA Cadence Cerebrus

cadence介绍

EDA仿真软件Cadence

--------------------------------------------------------------------------------

Cadence Design Systems Inc.是全球最大的电子设计技术(Electronic Design Technologies)、程序方案服务和设计服务供应商。其解决方案旨在提升和监控半导 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473