cadence.spb.15.2. 文章 最新资讯

苹果终于修复新iMac显示问题:AMD 5700XT显卡拒绝背锅

- 花几万块买的iMac,显示问题越来越严重,苹果显然不可能置之不理,当然这也不是AMD显卡的质量问题。 苹果今天发布了macOS Catalina 10.15.7更新,其解决了macOS无法自动连接Wi-Fi的问题,它还修复了一个可能导致文件无法通过iCloud Drive同步的bug。 当然了,对于新的iMac用户来说,它修复了一个导致配备Radeon Pro 5700 XT的机器屏幕出现白色线的问题。 自8月份推出27英寸iMac以来,用户一直有关于图形故障的投诉,该型号包括更高端的5700

- 关键字: iMac AMD macOS Catalina 10.15.7

Cadence与联电合作开发28纳米HPC+工艺中模拟/混合信号流程的认证

- 联华电子今(6日)宣布Cadence®模拟/混合信号(AMS)芯片设计流程已获得联华电子28纳米HPC+工艺的认证。 透过此认证,Cadence和联电的共同客户可以于28纳米HPC+工艺上利用全新的AMS解决方案,去设计汽车、工业物联网(IoT)和人工智能(AI)芯片。 此完整的AMS流程是基于联电晶圆设计套件(FDK)所设计的,其中包括具有高度自动化电路设计、布局、签核及验证流程的一个实际示范电路,让客户可在28纳米的HPC+工艺上实现更无缝的芯片设计。Cadence AMS流程结合了经客制化确认的类比

- 关键字: Cadence 联电 28纳米HPC 工艺中模拟/混合信号 流程认证

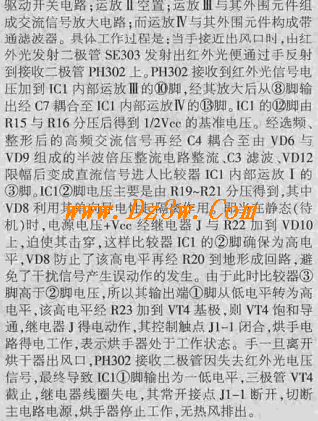

瑞萨电子推出业界领先性能15 Mbps光电耦合器,应对恶劣工业应用环境

- 2019 年 7 月 23 日,日本东京讯 - 全球领先的半导体解决方案供应商瑞萨电子株式会社(TSE:6723)今日宣布推出三款全新15Mbps光电耦合器,用于应对工业及工厂自动化设备的恶劣工作环境。在追求更高电压、紧凑型系统的趋势下,需要更严格的国际安全标准和环保解决方案,而这些解决方案则要求更小IC及更低功耗。RV1S9x60A系列拥有最佳的低阈值输入电流(IFHL)额定值:RV1S9160A(SO5)工作电流为2.0mA,RV1S9060A(LSO5)为2.2mA,RV1S9960A(LSDIP8

- 关键字: 瑞萨电子 15 Mbps光电耦合器 工业应用环境

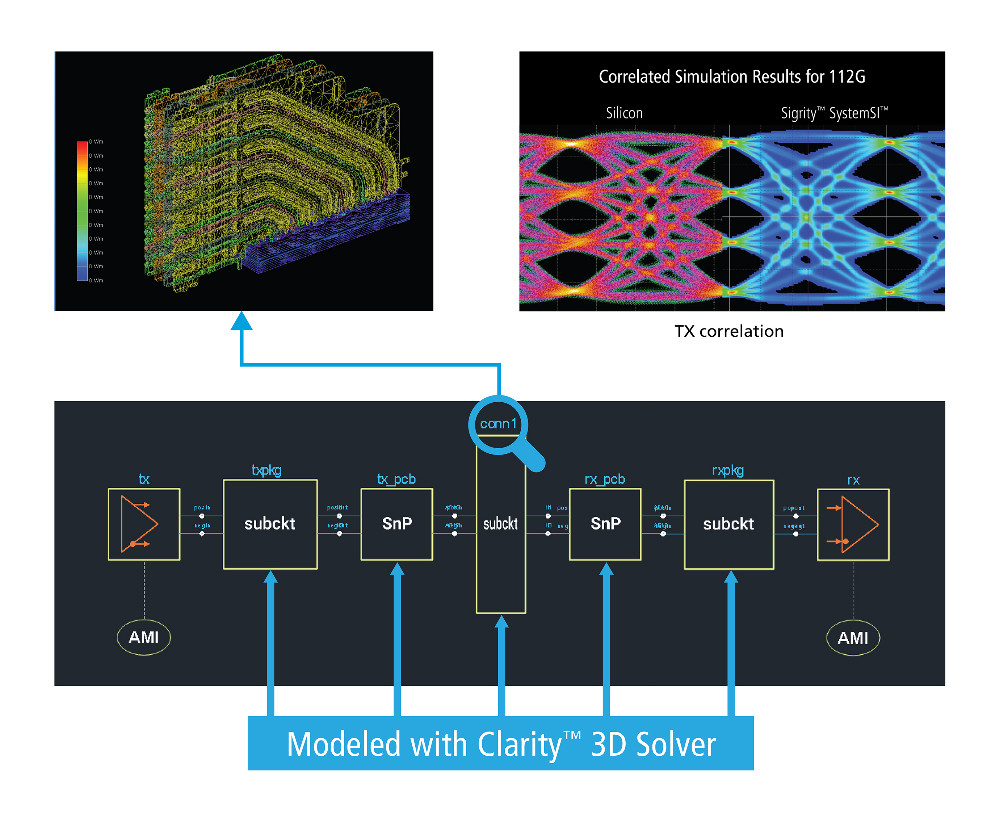

Cadence推出Clarity 3D场求解器,为系统级分析和设计提供前所未有的性能及容量

- 内容提要: • Clarity 3D Solver场求解器是Cadence系统分析战略的首款产品,电磁仿真性能比传统产品提高10倍,并拥有近乎无限的处理能力,同时确保仿真精度达到黄金标准 • 全新的突破性的架构针对云计算和分布式计算的服务器进行优化,使得仿真任务支持调用数以百计的CPU进行求解 • 真正的3D建模技术,避免传统上为了提高仿真效率而人为对结构进行剪切带来的仿真精度降低的风险 • 轻松读取所有标准芯片和IC封装平台的设计数据,并与Cadence设计平台实现专属集成

- 关键字: Cadence Cadence® Clarity™ 3D Solver场求解器

Zigbee框架体系结构及组网技术的研究及应用

- 摘要:基于Zigbee网络的分层网络框架体系结构和以IEEE802.15. 4为基础的协议栈架构,采用理论介B和实验验证相结合的方法,首先对Zigbee网络框架结构

- 关键字: 物联网 IEEE802.15.4协议 网络自愈 数据采集

4周小白成为大神,速成Cadence Allegro 让你走向职场巅峰!

- 一、PCB工程师目前现状 近年来,随着工业4.0战略的实施,智能硬件的加速崛起,PCB工程师更是成为了未来最有前途的职业之一。特别是电子工业的不断壮大,使得产品研发周期不断缩短、信号速率不断提高、单板密度越来越大、门电路工作电压越来越低、SI-PI-EMI问题趋于复杂,这样就要求PCB设计工程师必须提高专业素养,也使得PCB设计的工作日益成为电子设计中独立而又不可缺失的一环。 二、作为一名Allegro工程师 面对电子设备这些高性能、高速、高密、轻薄的趋势,高速信号的PCB设计,越来越成为电子硬

- 关键字: Cadence

cadence.spb.15.2.介绍

您好,目前还没有人创建词条cadence.spb.15.2.!

欢迎您创建该词条,阐述对cadence.spb.15.2.的理解,并与今后在此搜索cadence.spb.15.2.的朋友们分享。 创建词条

欢迎您创建该词条,阐述对cadence.spb.15.2.的理解,并与今后在此搜索cadence.spb.15.2.的朋友们分享。 创建词条