cadence.spb.15.2. 文章

最新资讯

楷登电子(美国Cadence公司)宣布即将于8月22日(星期二)在上海浦东嘉里大酒店举办一年一度的中国用户大会——CDNLive China 2017。以“联结,分享,启发!”为主题的CDNLive大会将集聚超过1000位IC行业从业者,包括IC设计工程师、系统开发者与业界专家,将分享重要半导体设计领域的解决方案和成功经验,让参与者获得知识、灵感与动力,并为实现高阶半导体芯片、SoC设计和系统挑战提供解决方案。详细的会议信息及报名请浏览www.cdnlive.com CDNLiv

关键字:

Cadence CDNLive

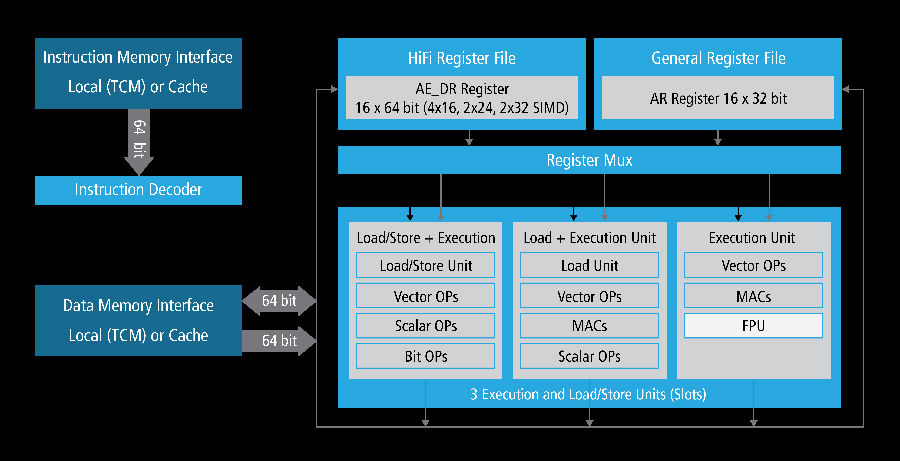

楷登电子(美国 Cadence 公司)今天宣布推出针对最新移动和家庭娱乐应用中系统级芯片(SoC)设计的Cadence® Tensilica® HiFi 3z DSP IP内核 。其应用包括智能手机、增强现实(AR)/ 3D眼镜、数字电视和机顶盒(STB)等。比较在业界音频DSP内核发货量站主导地位的前一代产品HiFi 3 DSP ,新的HiFi 3z架构将可提供超过1.3

关键字:

Cadence DSP

做芯片设计的各位,在某个时刻,你也许会产生一个想法,“为什么不自己设计一个处理器呢?”或许是手头的处理器并不好用;或许是想用的处理器贵的离谱;或许是你希望做出差异化的产品;又或者仅仅因为它是个诱人的挑战,你想尝试一下...既然如此,我很高兴能和你讨论一下怎么完成这个任务。 交付物 我们先从结果说起,也就是这项任务的最终交付物。这里不妨参考ARM处理器核的deliverables。当然,如果只是一个自己用的专用处理器,不一定要有这么完整的交付物。 硬件:主要是处理器相关的RTL代码,验证环境,ED

关键字:

专用处理器 Cadence

楷登电子(美国Cadence公司)今日正式发布全新VirtualBridge™适配器。较传统RTL仿真,基于虚拟仿真技术的VirtualBridge™适配器可以加速硅前验证阶段的软件初启。同时,VirtualBridge适配器与传统在线(In-Circuit)仿真应用模式互为补充,通过Cadence® Palladium® Z1企业级仿真平台,可以让软件设计师提前3个月开始进行硅前软件验证工作。如需了解更多内容,请访问www.cadence.com/go/virtualbridge

关键字:

Cadence VirtualBridge

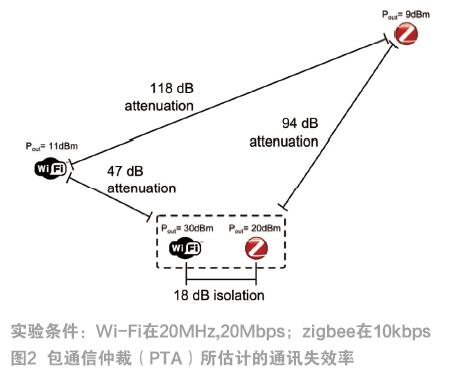

ZigBee无线技术和IEEE802.15.4能为功率受制约的无线应用提供所需的成本、性能和可靠性要求。由于ZigBee的技术优点和商业潜能,它已获得广泛的业内支持。

关键字:

ZigBee IEEE802.15.4

楷登电子(美国Cadence公司)今日发布全新Cadence® Virtuoso® System Design Platform(Virtuoso系统设计平台),结合Cadence Virtuoso平台与Allegro® 及Sigrity™技术,打造一个正式的、优化的自动协同设计与验证流程。多项跨平台技术的高度集成帮助设计工程师实现芯片、封装和电路板的同步和协同设计。这一过程在此之前只能通过手动完成,全新Virtuoso系统设计平台可以实现流

关键字:

Cadence Virtuoso

摘 要:本文对基于IEEE802.15.4 协议全功能节点FFD(Full Function device or Coordinator)进行了研究,给出了节点的硬件结构和软件设计。节点以8 位AVR

关键字:

IEEE802.15.4 无线传感器网络 AVR

楷登电子(美国Cadence公司)今日正式发布JasperGold® 形式验证平台扩展版,引入高级形式化验证技术的JasperGold Superlint和Clock Domain Crossing (CDC)应用,以满足JasperGold形式验证技术在RTL设计领域的签核要求。较现有验证解决方案,Superlint和CDC应用提高了IP设计质量,后期RTL变更最高减少80%, IP开发时间缩短4周。如需了解更多关于JasperGold技术

关键字:

Cadence RTL

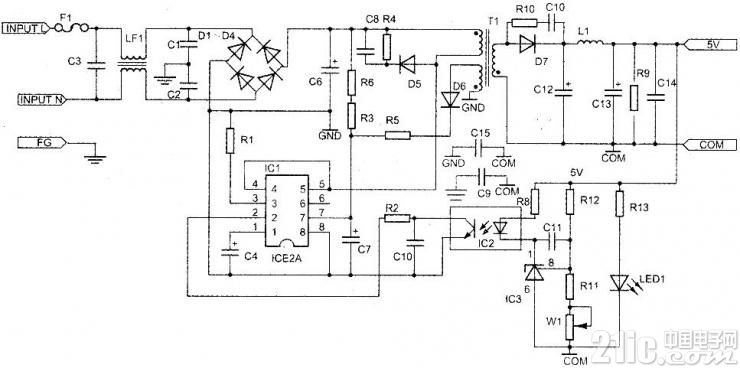

由于人们日益渴望通过智能手机、TV、GPS 和 Wi-Fi 传送数据,所以通信基础设施的有限带宽几乎被填满了。为了满足这种渴望,通信设计师定义了各种系统,将越来越多的数据塞进有限的带宽中,不过数据传输速率的提高是有代价的:需要保真度越来越高的发送和接收信号链路。

关键字:

RF/IF放大器 LTC6431-15 LTC6430-15

楷登电子(美国 Cadence 公司) 今日宣布其数字、签核与定制/模拟工具成功在三星电子公司7LPP和8LPP工艺技术上实现。较前代高阶工艺节点FinFET技术,7LPP和8LPP工艺技术不仅进一步优化了功耗、性能和面积特性,扩展能力也更为出色。目前,客户已经可以应用下一代技术开始早期设计。 Cadence定制/模拟、数字和签核工具全面满足三星工艺需求,支持实现7LPP和8LPP工艺技术;三星客户可开发各类复杂的高阶节点设计,充分满足移动市场和其他垂直市场的应用需求。

关键字:

Cadence 7LPP

作者 王莹 近日,Cadence发布了首款面向汽车、监控、无人机和移动市场的神经网络DSP IP,引起了业界的关注。 Cadence公司Tensilica事业部资深市场群总监Steve Roddy专程来到北京,向媒体介绍其特点。 在神经网络的器件方面,英伟达主宰了通用GPU。此次Cadence Tensilica发布的神经网络DSP IP则是面向嵌入式芯片。 通常其他友商的方案是面向一个卷积神经网络(CNN)层,而最新的Cadence Tensilica Vision C5 DSP由于可配置,可以面

关键字:

Cadence 神经网络DSP IP Steve Roddy 201706

近日,Cadence发布了首款面向汽车、监控、无人机和移动市场的神经网络DSP IP,引起了业界的关注。 实际上,多家公司正在推出或研制神经网络IP、c/解决方案。Cadence的方案有何优势?Cadence公司Tensilica事业部资深市场群总监Steve Roddy为此专程来到北京,向媒体介绍其特点。 Vision C5概况 在神经网络的器件方面,英伟达主宰了通用GPU。此次Cadence Tensilica发布的神经网络DSP IP则是面

关键字:

Cadence 芯片

楷登电子(美国Cadence公司)今日正式公布业界首款独立完整的神经网络DSP —Cadence® Tensilica® Vision C5 DSP,面向对神经网络计算能力有极高要求的视觉设备、雷达/光学雷达和融合传感器等应用量身优化。针对车载、监控安防、无人机和移动/可穿戴设备应用,Vision C5 DSP 1TMAC/s的计算能力完全能够胜任所有神经网络的计算任务。如需了解更多内容,请参访www.cadence.co

关键字:

Cadence DSP

楷登电子(美国 Cadence 公司)今日宣布,凭借Cadence® ProtiumÔ S1 FPGA原型验证平台,晶晨半导体(Amlogic)成功缩短其多媒体系统级芯片(SoC)设计的上市时间。基于Protium S1平台,晶晨加速实现了软/硬件(HW/SW)集成流程,上市时间较传统软硬件集成工艺缩短 2 个月。如需了解Protium S1 FPGA原型设计平台的详细内容,请访问www.cadence

关键字:

Cadence Protium

cadence.spb.15.2.介绍

您好,目前还没有人创建词条cadence.spb.15.2.!

欢迎您创建该词条,阐述对cadence.spb.15.2.的理解,并与今后在此搜索cadence.spb.15.2.的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473