全球知名的电子设计创新领导者Cadence设计系统公司今日宣布为台积电16纳米FinFET+ 制程推出一系列IP组合。 Cadence所提供的丰富IP组合能使系统和芯片公司在16纳米FF+的先进制程上相比于16纳米FF工艺,获得同等功耗下15%的速度提升、或者同等速度下30%的功耗节约。

目前在开发16 FF+工艺的过程中,Cadence的IP产品组合包括了在开发先进制程系统单芯片中所需的多种高速协议,其中包括关键的内存、存储和高速互联标准。IP将在2014年第四季度初通过测试芯片测试。有关IP

关键字:

Cadence 台积电 FinFET

全球知名电子设计创新领先公司Cadence设计系统公司今日宣布,其数字和定制/模拟分析工具已通过台积电公司16FF+制程的V0.9设计参考手册(Design Rule Manual,DRM) 与SPICE认证,相比于原16纳米FinFET制程,可以使系统和芯片公司通过此新工艺在同等功耗下获得15%的速度提升、或者在同等速度下省电30%。目前16FF+ V1.0认证正在进行中,计划于2014年11月实现。Cadence也和台积电合作实施了16FF+ 制程定制设计参考流程的多处改进。此外,Cadence也

关键字:

Cadence 台积电 FinFET

全球知名电子设计创新领先公司Cadence设计系统公司,今日宣布台积电采用了Cadence®16纳米FinFET单元库特性分析解决方案。由Cadence和台积电共同研发的单元库分析工具设置已在台积电网站上线,台积电客户可以直接下载。该设置是以Cadence Virtuoso® Liberate® 特性分析解決方案和Spectre® 电路模拟器为基础,并涵盖了台积电标准单元的环境设置和样品模板。

利用本地的Spectre API整合方案,Liberate和Spect

关键字:

Cadence 台积电 FinFET

在高密度互联技术中,PCB规模比较大,需要进行团队合作,接下来,给大家介绍一种合作开发的方法。

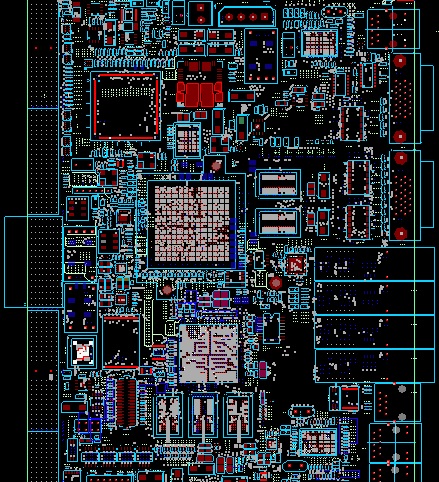

如图1,为我们需要合作的PCB板。

图1

在图1的中心部分,有一片比较大的FPGA芯片,如果想将该部分的布局、布线让另外一个同事处理,自己集中精力把其他部分的搞定。那么该怎么办呢?点击place->Design Partition,然后点击create partition,首先划定一块区域。划定区域的方法有以下几种:Add rectangle和Add sh

关键字:

cadence PCB

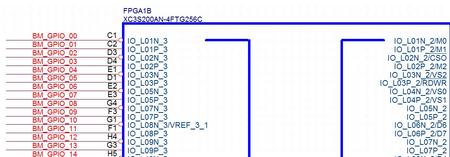

有好几个同事问我cadence之capture中关于保存元器件封装的问题。

我们知道,封装库的管理是非常重要的事情,是我们所有工程设计的基础,封装库有一丁点的错误,可能辛苦几个月的设计就白费了,比如:电源管脚、地管脚定义错、地址线数据线接反、多定义管脚、少定义管脚等(原理图封装如此,PCB封装也不例外),所以针对比较复杂的元器件,比如FPGA、CPU,动辄上千个管脚,如果自己一个管脚一个管脚画的话,再加上核对的时间,可能需要一周时间,并且还容易出错。这时候拿来主义就用到了,别人成熟的封装,调试没

关键字:

cadence capture PCB

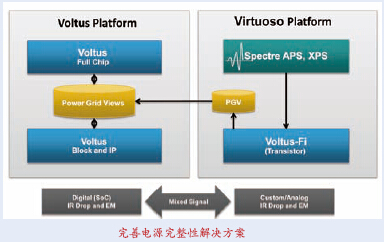

8月5日,Cadence公司在上海隆重举办年度CDNLive使用者大会。期间,Cadence宣布推出Voltus-Fi定制型电源完整性解决方案,芯片签收与验证部门产品营销总监Jerry Zhao向行业媒体具体讲解了新产品的特点。

VoltusTM-Fi定制型电源完整性解决方案具备晶体管级的电迁移和电流电阻压降分析技术(EMIR),获得晶圆厂在电源签收中SPICE级精度的认证,从而创建了设计收敛的最快路径。新的解决方案采用Cadence Spectre® APS(Accelerated P

关键字:

Cadence Voltus-Fi SPICE 201409

全球电子设计创新领先公司Cadence设计系统公司 (Cadence Design Systems, Inc) 在上海浦东嘉里大酒店举办年度CDNLive使用者大会,会议集聚了Cadence的技术用户、开发者、业界专家与行业媒体700多人,Cadence工具的开发专家和使用者们面对面分享重要设计与验证问题的解决经验,探讨高级晶片、SoC和系统的技术潮流趋势。

5号早上,Cadence公司副总裁兼中国区总经理刘国军先生首先代表公司欢迎业界客户、合作伙伴、专家学者及媒体朋友的到来。Cadence总裁

关键字:

Cadence CDNLive SoC

全球电子设计创新领先公司Cadence设计系统公司今天宣布推出Cadence® Voltus™-Fi定制型电源完整性解决方案(Cadence® Voltus™-Fi Custom Power Integrity Solution),具备晶体管级的电迁移和电流电阻压降分析技术(EMIR),获得晶圆厂在电源签收中SPICE级精度的认证,从而创建了设计收敛的最快路径。新的解决方案采用Cadence Spectre® APS(Accelerated Parall

关键字:

Cadence Voltus-Fi EMIR

电子产品世界,为电子工程师提供全面的电子产品信息和行业解决方案,是电子工程师的技术中心和交流中心,是电子产品的市场中心,EEPW 20年的品牌历史,是电子工程师的网络家园

关键字:

零中频放大器 低噪声 DIS管脚 Cadence

全球电子设计创新领先企业Cadence设计系统公司(NASDAQ: CDNS)于2014年5月20日宣布,立即推出基于台积电16纳米FinFET制程的DDR4 PHY IP(知识产权)。16纳米技术与Cadence创新的架构相结合,可帮助客户达到DDR4标准的最高性能,亦即达到3200Mbps的级别,相比之下,目前无论DDR3还是DDR4技术,最高也只能达到2133Mbps的性能。通过该技术,需要高内存带宽的服务器、网络交换、存储器结构和其他片上系统(SoC)现在可以使用Cadence® DD

关键字:

Cadence DDR4 PHY IP CRC

全球电子设计创新领先企业Cadence设计系统公司(NASDAQ: CDNS)于2014年5月13日宣布,海思半导体(HiSilicon Semi)进一步扩大采用Cadence® Palladium® XP 验证运算平台作为其仿真方案,运用于移动和数字媒体System-on-Chip (SoC) 与 ASIC开发。

海思提供通信网络和数字媒体的ASICs 和 SoCs,包括网络监控,视频电话,数字视频广播与IPTV解决方案。这些市场的解决方案需要高水准质量与经得起磨练的硬件软件验

关键字:

Cadence ASICs SoCs

摘要:为了解决高速多层PCB的电源完整性问题,缩短其开发周期,提高其工作性能,以ARM11核心系统为例,提出利用Cadence PI对PCB进行电源完整性分析的方法。通过对电源系统目标阻抗分析,确定去耦电容的数值,数量以及布局;对电源平面进行直流压降和电流密度分析,改善PCB设计,优化系统的电源完整性。利用动态电子负载搭建的测试平台,对电源仿真分析后制作的PCB进行测试,系统电源完整性较好,表明分析的结果是有效的。

随着现代高速信号的速率越来越快,信号边缘越来越陡,芯片的供电电压的进一步降低,时钟频率和

关键字:

Cadence

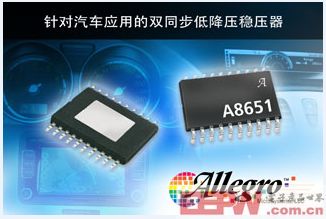

Allegro MicroSystems, LLC 公司宣布推出针对多输出系统的新型双转换器。Allegro’经 AEC-Q100 标准认证的 A8651 是双 2 A 低 VIN 同步稳压器,带可调频率,整合了高端 P 通道 MOSFET 和低端 N 通道 MOSFET。A8651 整合电流模式控制,可

关键字:

Allegro 双转换器 MOSFET

全球电子设计创新领先企业Cadence设计系统公司日前宣布,展讯通信有限公司(Spreadtrum Inc.)选择Cadence® Palladium® XP II验证计算平台用于系统芯片(SoC)验证和系统级验证。展讯使用Palladium XP II的目的是为了缩短芯片的研发周期,并进一步提高其移动芯片开发效率。上述芯片主要用于智能手机、功能手机和消费类电子产品。 “在竞争异常激烈的移动手持设备市场上,功耗低与上市

关键字:

Cadence Incisive Palladium

Xilinx, Inc. 与 Cadence 设计系统公司日前宣布共同合作开发了业界首个用于在硬件成型之前对基于Xilinx Zynq™-7000可扩展式处理平台(EPP)系统进行系统设计、软件开发与测试的虚拟平台。该方案进一步改善了Xilinx的基于ARM®处理器平台的开发环境,为嵌入式软件设计师改善了开发流程,让软件内容能够驱动硬件设计。 “从2008年开始,Xilinx已经为Zynq-7000 EPP设计了一套全面的开发工

关键字:

Xilinx Zynq-7000 Cadence

cadence-allegro介绍

您好,目前还没有人创建词条cadence-allegro!

欢迎您创建该词条,阐述对cadence-allegro的理解,并与今后在此搜索cadence-allegro的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473