- 全球电子设计创新领先企业Cadence设计系统公司(NASDAQ:CDNS)将分别于9月10日、12日在北京金隅喜来登酒店和上海浦东嘉里大酒店举办“CDNLive用户大会”。此会议集聚中国产业链高阶主管、Cadence的技术使用者、开发者与业界专家,分享重要设计与验证问题的解决经验,并为实现高阶芯片、SoC和系统、IP及工具的新技术发现新技术。

- 关键字:

Cadence SoC

- Cadence设计系统公司与上海华力微电子有限公司,今天共同宣布华力微电子基于Cadence Encounter数字技术交付出55纳米平台的参考设计流程。从现在起,华力微电子首次在其已建立的55 纳米工艺平台上实现了从 RTL到GDSII的完整流程,它也是Cadence与上海华力紧密合作的结果。

在该流程中所使用的Cadence数字工具包括RTL Compiler、Encounter Digital Implementation 系统、Conformal LEC、QRC Extraction、E

- 关键字:

Cadence 55纳米

- 全球电子设计创新领先企业Cadence设计系统公司(NASDAQ:CDNS)日前宣布,瑞昱半导体公司(Realtek Semiconductor Corp)获得Cadence Tensilica(Cadence® Tensilica®)授权,可使用HiFi 音频/语音DSP(数字信号处理器)IP内核,配合Sensory公司(IC和嵌入式软件解决方案提供商)的TrulyHandsFree™方案一起,用以实现长时开启(Always-on)语音控制与识别技术。

- 关键字:

Cadence 瑞昱 DSP

- 全球电子设计创新领先企业Cadence设计系统公司(NASDAQ:CDNS)与上海华力微电子有限公司,日前共同宣布华力微电子基于Cadence ® Encounter® 数字技术交付出55纳米平台的参考设计流程。从现在起,华力微电子首次在其已建立的55 纳米工艺平台上实现了从 RTL到GDSII的完整流程,它也是Cadence与上海华力紧密合作的结果。

- 关键字:

Cadence 华力 纳米

- 全球电子设计创新领先企业Cadence设计系统公司(NASDAQ:CDNS)日前宣布推出全新用于PCIe 3.0的SpeedBridge® Adapter。它为设计师们提供了一个重要的工具,来验证和确认他们的PCI Express (PCIe) 设计。

- 关键字:

Cadence PCIe SoC

- Allegro MicroSystems - 公司宣布增添一款新型 LED 驱动器 IC,以完善其符合标准的现有汽车 LED 驱动器 IC 产品组合。Allegro 的 A6269 是一款线性、可编程电流调节器,其从两个输出中的每一个均可提供最高 200 mA 的电流,以驱动高亮 LED 阵列。

- 关键字:

Allegro LED 驱动器

- 益华电脑(Cadence Design Systems)近日宣布两项成功合作案例,其一为设计服务业者创意电子(GUC)运用Cadence Encounter数位设计实现系统(Digital Implementation System,EDI)与Cadence Litho Physical Analyzer,成功地完成了20nm系统晶片(SoC)测试晶片的试产。此外晶圆代工大厂联电(UMC)已经采用Cadence 「设计中(in-design)」与signoff DFM (design-for-manufa

- 关键字:

Cadence 制程设计

- 全球电子设计创新领先企业Cadence设计系统公司(NASDAQ:CDNS)日前宣布,历经广泛的基准测试后,半导体制造商联华电子(NYSE:UMC;TWSE:2303)(UMC)已采用Cadence® “设计内”和“签收”可制造性设计(DFM)流程对28纳米设计进行物理签收和电学变量优化。

- 关键字:

联华电子 Cadence DFM

- 全球电子设计创新领先企业Cadence设计系统公司(NASDAQ:CDNS) 日前宣布推出用于实现电学感知设计的Virtuoso®版图套件,它是一种开创性的定制设计方法,能提高设计团队的设计生产力和定制IC的电路性能。

- 关键字:

Cadence Virtuoso EAD

- 为专注于解决先进节点设计的日益复杂性,全球电子设计创新领先企业Cadence设计系统公司(NASDAQ:CDNS) 日前宣布,台积电已与Cadence在Virtuoso定制和模拟设计平台扩大合作以设计和验证其尖端IP。

- 关键字:

Cadence Virtuoso 台积 PDKs

- 全球电子设计创新领先企业Cadence设计系统公司(NASDAQ:CDNS) 日前宣布,设计服务公司创意电子(GUC)使用Cadence® Encounter®数字实现系统(EDI)和Cadence光刻物理分析器成功完成20纳米系统级芯片(SoC)测试芯片流片。双方工程师通过紧密合作,运用Cadence解决方案克服实施和可制造性设计(DFM)验证挑战,并最终完成设计。

- 关键字:

Cadence DFM

- Cadence Encounter数字实现系统与Cadence光刻物理分析器

可降低风险并缩短设计周期

全球电子设计创新领先企业Cadence设计系统公司(NASDAQ:CDNS) 今天宣布,设计服务公司创意电子(GUC)使用Cadence? Encounter?数字实现系统(EDI)和Cadence光刻物理分析器成功完成20纳米系统级芯片(SoC)测试芯片流片。双方工程师通过紧密合作,运用Cadence解决方案克服实施和可制造性设计(DFM)验证挑战,并最终完成设计。

在开发过程中

- 关键字:

Cadence 20纳米 SoC

- Allegro中尺寸标注有很强大的功能,包括线性标注,角度标注,引线标注等。下面介绍一下Allegro中尺寸标注参数的设置。执行Manufacturendash;Dimension/Draftndash; Parameters,会弹出下图对话框1. Standard Confo

- 关键字:

Allegro 尺寸 标注 参数

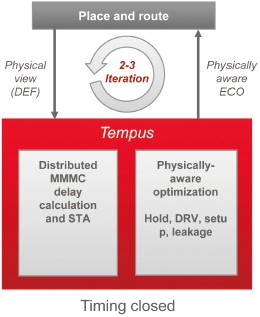

- 为简化和加速复杂IC的开发,Cadence 设计系统公司不久前推出Tempus时序签收解决方案。这是一款新的静态时序分析与收敛工具,旨在帮助系统级芯片 (SoC) 开发者加速时序收敛,将芯片设计快速转化为可制造的产品。

- 关键字:

Cadence Tempus CPU 201307

cadence-allegro介绍

您好,目前还没有人创建词条cadence-allegro!

欢迎您创建该词条,阐述对cadence-allegro的理解,并与今后在此搜索cadence-allegro的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473