cadence之器件原理封装的提取

有好几个同事问我cadence之capture中关于保存元器件封装的问题。

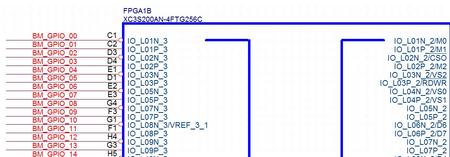

本文引用地址:https://www.eepw.com.cn/article/263538.htm我们知道,封装库的管理是非常重要的事情,是我们所有工程设计的基础,封装库有一丁点的错误,可能辛苦几个月的设计就白费了,比如:电源管脚、地管脚定义错、地址线数据线接反、多定义管脚、少定义管脚等(原理图封装如此,PCB封装也不例外),所以针对比较复杂的元器件,比如FPGA、CPU,动辄上千个管脚,如果自己一个管脚一个管脚画的话,再加上核对的时间,可能需要一周时间,并且还容易出错。这时候拿来主义就用到了,别人成熟的封装,调试没有问题,我们用着比较踏实。其实我们完全可以将别人的.olb库文件拿来自己调用。有几个同事直接拿来别人的.dsn原理图文件,想从这个文件中提取封装,但是总是不能成功,所以拿出来与大家分享。下图中这个FPGA芯片为欲提取的元器件:

首先点中该器件,右键点击edit part,

出现如下的界面:

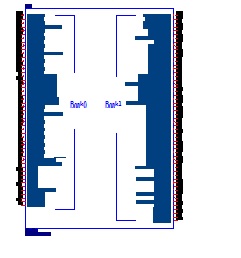

这个时候我们想将该器件存入到我们自己的原理库里面,但是save as老是灰色的,不让我们保存,好几个同事问我的时候都是这种情形,其实离成功只差一点点,看我的:

先不save as,而是点击view->package,出现如下界面,可以看到所有的part都显示出来了:

这个时候再点一下save as,怎么样,就可以看到可以让存储了,在弹出的对话框里选择存储路径、准备存入的库文件名称、以及自己给这个新器件的名字就可以了。

怎么样,看到这里,是不是自己也准备试一下啊,抓紧找个工程验证一下吧!

评论