随着SoC开发成本的不断增加,以及在SoC中实现多种功能整合的复杂性,很多无线、消费类电子的IC设计公司和系统公司开始采用“系统级封装”(SiP)设计以获得竞争优势。一方面是因为小型化、高性能、多用途产品的技术挑战,另一方面是因为变幻莫测的市场竞争。他们努力地节约生产成本的每一分钱以及花在设计上的每一个小时。相比SoC,SiP设计在多个方面都提供了明显的优势。 SiP独特的优势 SiP的优势不仅在于尺寸方面,SiP能够在更小的占用空间里提供更多的功能,并降低了开发成本和缩短了设计周

关键字:

SiP 封装 技术简介 封装

摘 要:为了能够实现通过集成所获得的优点,像高性能、低价格、较小的接触面、电源管理和缩短产品进入市场的时间,出现了针对晶圆级的系统级芯片(system on a chip简称SOC)和针对组件级的系统级组件(system on a pakage简称SOP)。本文介绍了SOC和SOP的益处、功能和优点。 关键词:封装技术;系统级芯片;系统级组件 1、引言

关键字:

SoC SoP 封装 封装

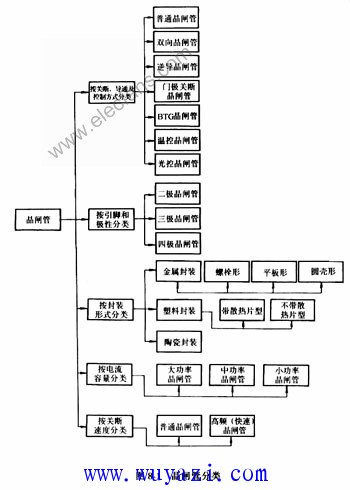

一、DIP双列直插式封装 DIP(DualIn-line Package)是指采用双列直插形式封装的集成电路芯片,绝大多数中小规模集成电路(IC)均采用这种封装形式,其引脚数一般不超过100个。采用DIP封装的CPU芯片有两排引脚,需要插入到具有DIP结构的芯片插座上。当然,也可以直接插在有相同焊孔数和几何排列的电路板上进行焊接。DIP封装的芯片在从芯片插座上插拔时应特别小心,以免损坏引脚。 DIP封装具有以下特点: &nb

关键字:

封装 芯片 封装

摘 要: 本文主要介绍了CPU芯片封装技术的发展演变,以及未来的芯片封装技术。同时,中可以看出芯片技术与封装技术相互促进,协调发展密不可分的关系。 关键词: CPU;封装;BGA 摩尔定律预测:每平方英寸芯片的晶体管数目每过18个月就将增加一倍,成本则下降一半。世界半导体产业的发展一直遵循着这条定律,以美国Intel公司为

关键字:

CPU SoC 封装 芯片 封装

第4届中国半导体封装测试技术与市场研讨会在成都召开,中国半导体行业协会封装分会理事长毕克允在开幕式上介绍说,虽然近年来封装业增长速度放缓,但封装测试行业在整个半导体产业链中的地位越来越突出。2005年我国IC总产量约300亿块,同比增长36.7%,销售收入750亿元,同比增长37.5%。IC封装测试方面,2005年IC封装总数量347.98亿块,销售收入351亿元。目前全球主要封测厂商大都已在中国建有生产基地。无论是本土厂商还是外资企业,新工艺的开发和成本的控制越来越受到厂商的重视

关键字:

封装 工艺成本 封装

随着VLSI工艺技术的发展,器件特征尺寸越来越小,芯片规模越来越大,数百万门级的电路可以集成在一个芯片上。多种兼容工艺技术的开发,可以将差别很大的不同种器件在同一个芯片上集成。为系统集成开辟了广阔的工艺技术途。 真正称得上系统级芯片集成,不只是把功能复杂的若干个数字逻辑电路放在同一个芯片上,做成一个完整的单片数字系统,而且在芯片上还应包括其它类型的电子功能器件,如模拟器件和专用存贮器,在某些应用中,可能还会扩大一些,包括射频器件甚至MEMS等。通常系统级芯片起码应在单片上包括数字系

关键字:

SoC 封装 系统级芯片集成 封装

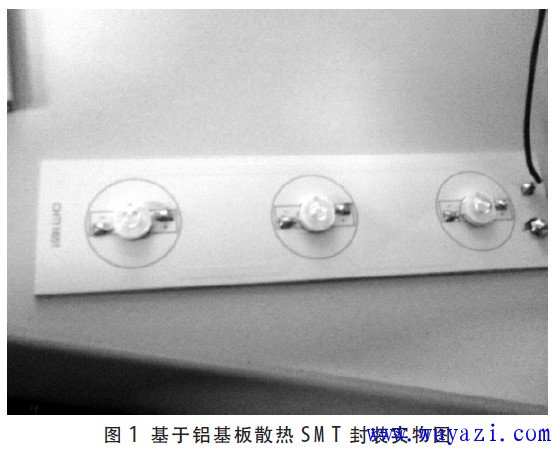

元件全部埋置于基板内部的系统集成封装 (Multi Device Sub-assemblie Embedding all Passive and Active Components in Substrate) 伴随轻薄短小、高性能便携电子设备的急速增加,将电子元器件埋置于基板内部的所谓后SMT(post-SMT)封装技术已初见端睨。目前,虽然是以埋置R、C、L等无源元件为主,但近年来,将芯片等有源元件,连同

关键字:

SoC 封装 高密度 封装

曾理,陈文媛,谢诗文,杨邦朝 (电子科技大学微电子与固体电子学院 成都 610054) 1 引言 数字化及网络资讯化的发展,对微电子器件性能和速度的需求越来越高,高阶电子系统产品,如服务器及工作站,强调运算速度和稳定性,而PC机和笔记本电脑对速度及功能需求也不断提高,同时,个人电子产品,如便携式多媒体装置、数字影像装置以及个人数字处理器(PDA)等的显著需求,使得对具有多功能轻便型及高性能电子器件的技术需求越来越迫切。此外,半导体技术已进

关键字:

SiP SoC 封装 集成电路 封装

摘 要:近年无线技术应用惊人发展,使得终端消费产品革新比以往任何一年都要频繁。 关键词:封装,SOC,贴片,射频 中图分类号:TN305.94 文献标识码:D 文章编号:l 004-一4507(2005)05—0045—02 1 封装技术的挑战 近年无线技术应用惊人发展,使得终端消费产品革新比以往任何一年都要频繁。手机产品的生命周期也变得越来越短了。为了实现这类产品的快速更新,电器技术方面的设计就不得不相应快速的简化。半导体产业提

关键字:

SiP SoC 半导体 封装 工艺技术 封装

所谓“封装技术”是一种将集成电路用绝缘的塑料或陶瓷材料打包的技术。以CPU为例,我们实际看到的体积和外观并不是真正的CPU内核的大小和面貌,而是CPU内核等元件经过封装后的产品。 封装对于芯片来说是必须的,也是至关重要的。因为芯片必须与外界隔离,以防止空气中的杂质对芯片电路的腐蚀而造成电气性能下降。另一方面,封装后的芯片也更便于安装和运输。由于封装技术的好坏还直接影响到芯片自身性能的发挥和与之连接的P

关键字:

名词解释 封装

概要:夏普微电子设计了一系列基于ARM 内核的片上系统(SoC ),旨在解决目前设计领域那些最有挑战性的问题,其中包括如何平衡高性能与低功耗等。本文对这些设计中的难题进行了回顾,并且在夏普基于ARM720TTM 的Blue Streak SoC 的基础上,介绍了一些解决方案。

新一代PDA 正在越来越受到人们的关注。从简单的个人信息管理(PIM )到商用无线销售终端(POS ),在这些复杂设

关键字:

SoC 半导体 封装 设计 封装

本文介绍在现代片上系统(SoC) 设计中使用开放式内核协议(OCP) ,解释了为什么标准的工业套接口在富有竞争性的 SoC设计很重要,说明了OCP 如何实现接口功能。讨论中说明了加速SoC设计以满足更短的上市时间的必要性,和复用IP 的优势。最后,本文讨论了三种不同的实现方法,阐明OCP 给半导体内核设计带来的灵活性。

问题 近年来,半导体工艺的改进和日益增长的市场压力使上市时间和设计重用成为半导体工业的热门话题。显然,减少SoC 设计周期可以减少上市时

关键字:

SoC Socket 半导体 封装 封装

SoC 还是 SiP?随着复杂系统级芯片设计成本的逐步上升,系统级封装方案变得越来越有吸引力。同时,将更多芯片组合到常规外形的单个封装中的新方法也正在成为一种趋势。

要 点

多裸片封装是建立在长久以来确立的提高电路密度的原则基础上的。用90nm工艺开发单片系统ASIC 的高成本促使人们研究多芯片的替代方案。很多雄心勃勃3D芯片封装的前兆是用

关键字:

SiP SoC 封装 芯片 封装

倡导和实现芯片封装协同设计的努力已经持续很多年了。随着90 nm工艺技术逐渐进入量产阶段,芯片与封装的同步设计才开始真正变成现实。这种转变的一个迹象是处于该领域的两家公司,Optimal和Rio Design Automation最近宣布了一项联合开发计划。 这项计划的目的是为90 nm节点的协同设计完成框架性工作。两家公司目前提供的设计工具都与其他大规模EDA公司的工具兼容。该项计划的主要驱动力来自于在芯片设计的起始阶段可以并行进

关键字:

封装 协同设计 芯片 封装

2004年11月在IMAPS召开的国际微电子研讨会上,SiP协会的研究者展示了他们正在开发的最新技术,这种新的技术能增加堆叠芯片封装的可选数量,他们的一体式单封装系统采用的是线上芯片技术,这种技术不需要金字塔形的堆叠,它允许使用V形堆叠,从而增加无源芯片集成的选择数量。 堆叠封装主要用于节省空间,即那些芯片彼此之间或与芯片外界之间不需要进行高密度互连的情形。采用堆叠的方式能节省空间并节约封装费用。通常的情况下,芯片排列一般采用金字塔形式(见图),因为采用这种形式,金线键合能十分容易进行

关键字:

封装

2.5d 封装介绍

您好,目前还没有人创建词条2.5d 封装!

欢迎您创建该词条,阐述对2.5d 封装的理解,并与今后在此搜索2.5d 封装的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473