基于最佳接收的UART的设计与实现

为了保证接收器能抵御一定程度的干扰而 进行正确的同步,检测同步的门限不能取N。假定同步检测的门限定为(N-3),则会出现这样的问题:如果接收到的信号波形良好,而又采用(N-3)作为检测同步门限,则同步模块得到的判决信号实际上偏离了数字相关器的最佳判决时刻,使判决器误判的可能性增加。较好的解决办法是增大单个码元周期内的采样次数N,使同步检测门限(N-3)与判决器判决门限N/2有较大距离,从而使后端的判决器有更好的抗干扰性能。根据实际测试的经验,取N为16,以13作为同步检测门限,以8作为判决门限。这样既能有效防止因干扰而造成的漏同步,又能保证后端的数据判决有较好的抗干扰性能。

本文引用地址:https://www.eepw.com.cn/article/83208.htm由上所述,同步模块实际上是对接收到的16个采样值进行译码,当有13个0时表示检测到同步,并将此时得到的判决信号提供给后端的判决器进行数据判决。在物理上这就是一个16输入的组合电路。由于FPGA有丰富的时序逻辑资源而缺乏组合逻辑资源,因此该电路模块若是在FPGA上实现要耗用大量的逻辑资源,所以需要对该模块的逻辑设计进行优化。

逻辑优化的原则是充分利用FPGA 逻辑资源丰富的特点,以相同功能的时序电路替代这个庞大的组合电路。如图8所示,输入信号RXD经过D触发器采样并经过一个反相器后做为使能信号送给下一级的模13计数器(即对D触发器采样得到的低电平计数),这样就可以用时序统计逻辑来替代原来的组合统计逻辑。对FPGA,这样的时序电路只需要耗用少数几个D触发器,可以极大地节省资源。然而时序统计逻辑可能会由于对随机脉冲干扰带来的反常低电平的采样积累而产生误同步,所以需要同时对输入信号RXD经过D触发器的采样得到的高电平进行计数。若得到连续多个不同长度(图7中长度为8)的高电平,则说明正在接收的不是Sync位,即使采样得到了低电平,也是干扰信号,这时就要对模13计数器复位,以防止干扰(低电平的干扰)的累积产生误同步。

2.2 数字相关器的设计优化

数字相关器的数学表达式为:

这时乘法器实际上是不需要的,数字相关器的输出是最近的N(N=16)个输入采样(即输入信号RXD的采样)的叠加。输入信号RXD的采样是1比特量化,其值为逻辑1(高电平),或逻辑0(低电平)。所以对输入采样的叠加可以用计数器实现:逻辑1使计数器计数加1,逻辑0则保持计数器的值不变。这样,复杂的数字相关器就可以用一个计数器实现。

图9为经过逻辑优化的数字相关器和判决器的电路。RXD经过D触发器(一个码元周期采样N=16 次)送入数字相关器。该数字相关器在逻辑设计上被优化为一个计数器,对D触发器输出的逻辑1进行统计计数。当同步模块送来判决信号时,判决器根据当时数字相关器的计数结果进行硬判决:计数结果≥8(N/2)即为逻辑1,否则为逻辑0(逻辑上把计数结果的Count[3]和Count[4]作逻辑或运算为抽样判决结果输出)。判决信号同时还要对数字相关器(即计数器)复位,因为这同时是新码元接收周期的开始,使数字相关器重新进行计数叠加。

3 基于FPGA的UART设计实现

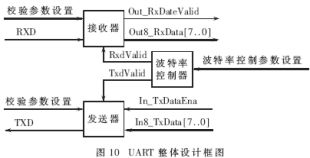

UART根据功能划分为波特率控制器、发送器和接收器三个模块。图10是UART的整体设计框图。Out8_RxData[7..0]和Out_RxDateValid是接收器收到数据后输出的数据及其使能信号。而In8_TxData[7..0]和In_TxDataEna是发送器要发送的数据及输入使能信号。校验参数设置包括是否需要校验、奇偶校验等。

3.1 波特率控制器的设计

波特率控制器根据波特率控制参数的设置,为接收器和发送器提供工作使能信号,这种工作使能信号的频率决定了UART工作的波特率。从逻辑设计的角度看,波特率控制器实质上是一个可变模计数器,波特率控制参数调整计数器的模,从而为接收器和发送器提供各种符合通信波特率要求的工作使能信号。

3.2 发送器的设计

发送器在接收到并行发送数据后,将数据进行并串变换,按照波特率控制器提供的工作使能信号的速率,将数据及奇偶校验位(是否发送校验位根据参数设置)逐位发送。发送器在逻辑设计上是一个有限状态机,图11是发送器状态跳转图。

3.3 接收器的设计

接收器的逻辑框图见图5,其中同步模块、数字相关器和判决器已详细介绍。下面介绍数据接收模块。数据接收模块负责将判决器的判决输出逐位接收,然后将接收到的串行位串转换成8位的字节,根据校验的参数进行设置。如果无需校验,则直接输出收到的字节;如果需要校验,则根据设置进行奇偶校验。如果校验显示接收有错误,则直接丢弃接收结果;如果校验无误,将收到的字节输出。数据接收模块在逻辑上也是由一个有限状态机实现,图12是数据接收模块的状态跳转图。

评论