基于混合信号的SIP模块应用

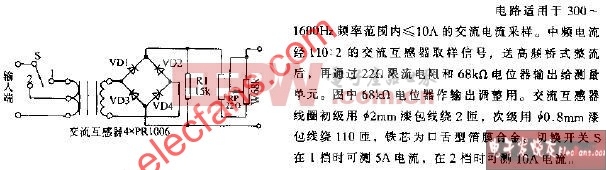

2.4采样电路部分

本文引用地址:https://www.eepw.com.cn/article/275682.htm信号处理模块采样保持电路部分将采样调零端口做引脚输出,可依据在此两端连接电阻对采样电路调零。采样保持电路输出端也做引脚输出,误差切换开关一输入端做引脚输入,系统工作时将采样保持输出和误差开关输入端口相连接,这样系统误差接入给运放参考端。

图5:混合信号模块采样保持电路外接端

2.5模拟输出说明

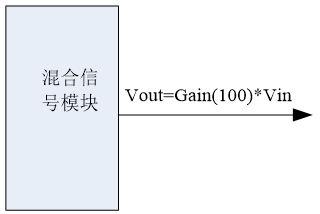

信号处理模块输出Vout=(Vin * Gain +Voffset )– Voffset,其中Vin= (Vin+ - Vin-), Voffset为系统误差由保持采样电路进行采集,Gain为差分运放增益本系统设置成100,可通过运放增益端进行调整。

整个系统在工作时可近似认为从开始工作到稳定运行整个过程,系统误差相等,从等式可以看出系统最终输出理想状态为输入信号Vin和放大倍数(模块设置成100倍)的乘积。

图6:混合信号模块输出

3电源说明

本模块芯片内部不含电源模块,所有电源输入为直接引脚灌入无转换。系统采用双电源供电为±12V,+5V、数字地GND、模拟地AGND,其中数字地和模拟地在模块内未进行连接。

图7:混合信号模块电源

4总结

评论