利用FPGA和分解器数字转换器简化角度测量

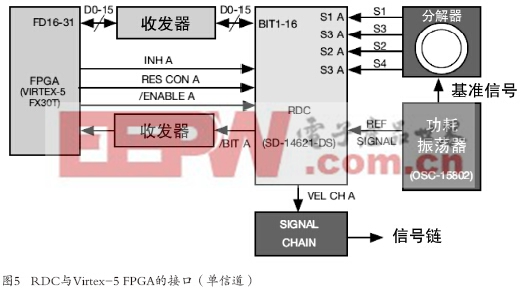

在本设计中采用赛灵思Virtex®-5 FX30T FPGA 。FPGA的I/O电压为3.3V,而RDC的电压为5V。因此我们采用电压收发器来实现这两个器件之间的电压兼容。通过赛灵思提供的GPIO IP核与FPGA建立内部连接,如图5所示。为了简单起见,图5仅显示一条具有一个分解器接口的信道。

6 器件驱动程序详细说明

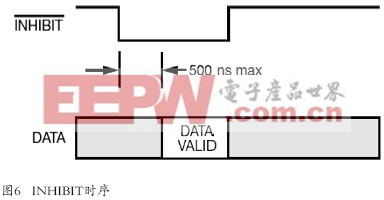

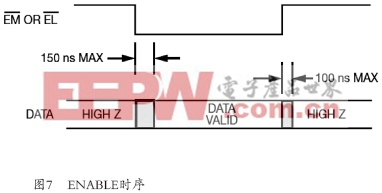

在本例中,FPGA采用20MHz的外部输入时钟。此FPGA具有一个运行频率为200MHz的PowerPC 440硬核。RDC的时序图见图6与图7。

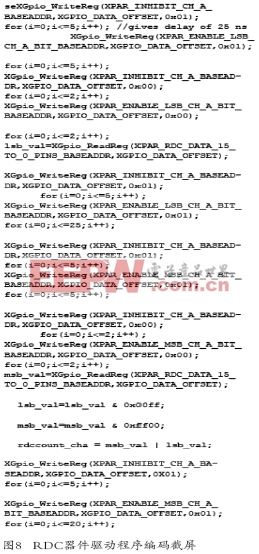

根据RDC的时序图,我们开发、测试并验证了实际硬件的功能是否正确。器件驱动程序的实际编码包含在单独的XBD文件中。根据时序图,我们生成了用于回路的所需延迟。在200MHz运行速率下进行处理时,每个计数都对应5纳秒的延迟。

器件驱动程序有三部分编码:RDC初始化、控制信号的生成及从RDC信道A的读取、以及控制信号的生成及从RDC信道B的读取。RDC初始化是设置信号方向和缺省值的阶段。例如,利用以下语句,信号方向将设置为从FPGA“输出”到RDC。

XGpio_WriteReg(XPAR_RESOLUTION_CNTRL_CH_A_

BASEADDR,XGPIO_TRI_OFFSET,0x000);

下一个语句通过写入“0x3”来设置16位分辨率(即:拉高):

XGpio_WriteReg(XPAR_RESOLUTION_CNTRL_CH_A_

BASEADDR,XGPIO_DATA_OFFSET,0x03);

图8为编码截屏。注:为了简化,我们仅提供一条信道的编码。

我们已经看到,角度传感器可以帮助工程师创造更好的转轮,进而设计出众多更高效的机械装置。分解器是一种尤为有用的角度传感器,只要能够与FPGA正确配合和控制,其就能够帮助工程师打造出无与伦比的机械装置。

fpga相关文章:fpga是什么

尘埃粒子计数器相关文章:尘埃粒子计数器原理 脉冲点火器相关文章:脉冲点火器原理 数字滤波器相关文章:数字滤波器原理

评论