FPGA设计开发软件ISE使用技巧之:典型实例-增量式设计演示

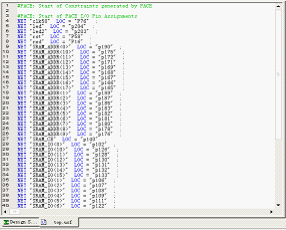

设置好管脚约束后,保存退出PACE。在“Processes for Source”中选择“Edit Constraints Text”,即在Text模式下编辑约束文件。可以看到系统自动生成的管脚约束文件内容,如图6.89所示。

本文引用地址:https://www.eepw.com.cn/article/269340.htm

图6.89 系统生成的管脚约束文件

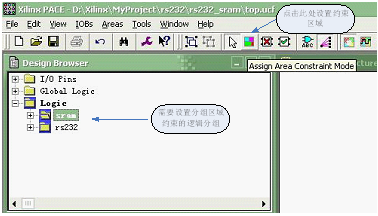

(4)设置分组区域约束。

在“Processes for Source”中选择“Create Area Constraints”,启动设置分组区域约束工具PACE。分别选中sram和rs232,单击左上角的

图6.90 进入分组区域约束模式

设置区域约束结果如图6.91所示。

图6.91 区域约束设置结果

如图6.91所示,图中左上角的区域对应的是SRAM逻辑分组的约束区域,右下角的区域为rs232逻辑分组的约束区域。采用如上的约束是综合两个逻辑分组内部逻辑的复杂性以及I/O位置来确定的。这里的约束并不惟一,读者可根据需要进行修改。

设置完毕后,保存设置。在“Processes for Source”中选择“Edit Constraints Text”,即在text模式下编辑约束文件,可看到在约束文件中新添了如下内容:

#PACE: Start of PACE Area Constraints

AREA_GROUP "AG_rs232" RANGE = SLICE_X0Y55:SLICE_X19Y38 ;//设置rs232逻辑分组区域

INST "rs232" AREA_GROUP = "AG_rs232" ;

AREA_GROUP "AG_sram" RANGE = SLICE_X34Y41:SLICE_X55Y18 ;//设置SRAM逻辑分组区域

INST "sram" AREA_GROUP = "AG_sram" ;

fpga相关文章:fpga是什么

评论