FPGA设计开发软件ISE使用技巧之:典型实例-ChipScope功能演示

(12)生成ILA核。

本文引用地址:https://www.eepw.com.cn/article/269339.htm单击图6.69中的“Generate Core”按钮,生成逻辑分析仪(ILA),如图6.70所示。

图6.67 设置触发参数对话框

图6.68 设置存储深度和数据位宽对话框

图6.69 设置生成实例的语言类型和综合工具

图6.70 生成ILA核

(13)将ICON和ILA插入设计。

完成上述步骤后就完成了集成控制核(ICON)和逻辑分析仪(ILA)的生成,系统生成的主要文件如表6.5所示。

表6.5 ChipScope生成文件列表

icon.edn集成控制器的网表文件

icon.ncf集成控制器的网表约束文件

icon_xst_example.v集成控制器的嵌入式例子代码

ila.end集成逻辑分析仪的网表文件

ila.ncf集成逻辑分析仪的网表约束文件

ila_xst_example.v集成逻辑分析仪的嵌入式例子代码

用户需要做的是根据提供的例程代码来修改自己的代码,将生成的集成控制核和集成逻辑分析仪插入到设计当中。具体修改时,需要在源文件中添加如下代码:

icon i_icon // ICON core instance,实例化ICON核

(

.control0 (control0)

);

wire [7:0] trig0;

ila i_ila // ILA core instance,实例化ILA核

(

.control (control0),

.clk (clk),

.trig0 (trig0)

);

assign trig0 = count;

从代码中可以看出要做的工作主要是实例化ICON核和ILA核。注意要将观察的信号(在这里为count)与ILA核的输入信号相连接,系统时钟与ILA核的时钟输入相连接,ICON的输出控制信号与ILA的输入控制信号相连接。这样就可以通过修改RTL代码来插入集成逻辑控制器和集成逻辑分析仪了。

(14)综合,布局布线,生成配置文件并下载。

具体的操作步骤可以参看2.6节的介绍,这里不再详述。需要注意的是ChipScope Pro要通过JTAG接口与器件连接。生成配置文件时,时钟要设置为JTAG Clock。

(15)启动ChipScope Pro Analyzer。

可通过直接运行“开始”/“程序”/“ChipScope Pro 8.2i”/“ChipScope Pro Analyzer”,也可以在ISE集成环境下,在进程浏览器中双击“Analyze Design Using ChipScope”启动。启动后界面如图6.71所示。

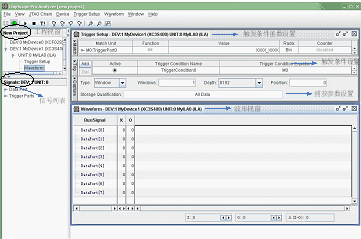

(16)打开JTAG连接。

单击

(17)设置触发条件。

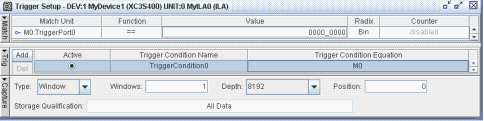

触发条件设置如图6.73所示。

图6.71 ChipScope Pro Analyzer用户界面

图6.72 成功连接后用户界面

图6.73 设置触发条件对话框

设置触发条件函数为“==”,数值为0000_0000(也就是说,触发端口的信号值为0000_0000时开始采集数据)。设置采集深度为8192。这里只有一个触发件M0,只需采用默认即可。当有多个条件时,要在“Trig”选项卡下设置起作用的正确条件,也可将触发条件设置为几个条件的逻辑组合。

fpga相关文章:fpga是什么

尘埃粒子计数器相关文章:尘埃粒子计数器原理

评论