零基础学FPGA(四)Verilog语法基基础基础(中)

7、结构语句

本文引用地址:https://www.eepw.com.cn/article/267552.htm(1)initial语句比较简单,这里就不多说了。

(2)always语句

always语句在仿真过程中是不断活动的,always语句后面的语句是否执行,这要看always语句是否满足触发条件。因此,always语句只有和时序控制语句结合才能使用,否则就会被死锁。例如:always areg=~areg;

这个always语句生成一个0延迟的无限跳变过程这时会发生死锁。但是一旦加上时序控制,这条语句就不一样了,例如:

always #10 areg=~areg;

这样的语句就描述的一个周期为20毫秒的跳变信号。所以我们常用这种方法来描述时钟信号,并作为激励信号来测试硬件电路。

看下面这个例子

reg [7:0] counter;

reg tick;

always @(posedge areg)

begin

tick=~tick;

counter=counter+1;

end

这个例子就是说每当信号areg上升沿到来时,信号tick取反,计数器counter加一,这种时间控制是always语句最常用的。

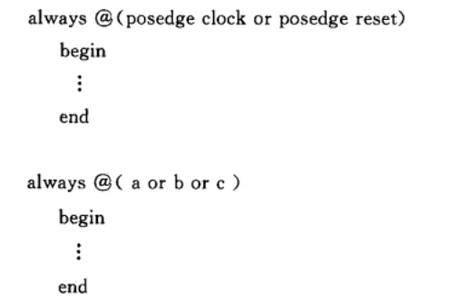

always语句的时间控制模板

如果组合逻辑块语句的输入变量过多容易漏掉,例如:

always @(a or b or c or d or e)

这样的情况下可以用always@ (*)语句来代替,*号自动将所有输入变量默认为敏感信号。

上面所讨论的都是等待信号的值发生变化或者触发时才执行相应语句,我们也可以用wait语句来用电平敏感来控制。例如

always

wait (count_enable) #20 count=count+1;

意思就是说,当count-enable的值为1时,程序延迟20毫秒后计数。

8、任务与函数

书上写了关于任务与函数的区别,写了好多,我觉得区别这两个概念主要看一点就够了,就是看有没有返回值,函数有,任务没有。举个例子

switch_bytes (old_bytes,new_bytes);这是个任务,没有返回值,功能是把新旧两个字节互换位置。

new_bytes=switch_bytes(old_bytes);这是个函数,功能是把旧字节转换后赋值给新字节。有返回值。

下面写一个交通信号灯的程序来学习一下任务这个概念

moudle xiaomo_traffic;

reg clock,red,green,amber;

//定义时钟,红灯,黄灯,绿灯

parameter on=1,off=0,red_tics=350.amber_tics=30,green_ics=200;

//定义红灯等待350个时钟,黄灯等待30个时钟,绿灯等待200个时钟

initial red=0;

initial green=0;

initial amber=0;

//初始化,这里用initial语句保证三条语句同时执行

always

begin

red=on; //红灯亮

light (red,red_tics); //这里用到任务,功能是等待350个时钟的时间,声明看下面程序

amber=on; //黄灯亮

light (amber,amber_tics); //等待30个时钟

green=on; //绿灯亮

light (green,green_tics); //等待200个时钟

end

task:light; //命名任务

output color;

input [31:0] tics;

//注意这里的两个变量要与上面的一一对应,也就是说上面的light(red,red_tics);中的red对应color,red_tics对应tics

begin

repeat(tics); //重复执行tics次下面的语句

@(posedge clock); //等待上升沿,因为这里的tics对应上面的red_tics几个,所以这里要等待相应个上升沿

color=off; //等到相应个上升沿结束时,相应颜色的灯关闭

end

endtask

//下面就是写时钟函数了,用always块

always

begin

#100 clock=0;

#100 clock=1; //每100毫秒产生一次跳变

end

endmoudle

注意:这个程序要找对一一对应关系,例如脉冲模块里的clock对应posedge clock中的clock,程序行与行之间是有联系的,不能随便声明

fpga相关文章:fpga是什么

c语言相关文章:c语言教程

评论