零基础学FPGA(四)Verilog语法基基础基础(中)

4、循环语句

本文引用地址:https://www.eepw.com.cn/article/267552.htmVerilog语法**有4中循环语句,这里只简单说一下C语言里没有的两种

(1) forever语句

连续执行语句,这种语句主要用在产生周期性的波形,用来做仿真信号。个人理解和always语句差不多的功能,但是,forever语句只能用在initial块中。

(2)repeat 语句后面接常量表达式,可以指定循环次数,例如;

repeat (8)

begin

…

end

表示循环8次相应语句。

5、顺序块和并行块

所谓顺序块就是前面说的begin…end,他的作用就是把多条语句组合到一起执行,在顺序块里面,语句是一条一条顺序执行的,如果遇到#10延迟语句,延迟也是相对于上一条语句的延迟,这一点比较重要。

相对于顺序块的就是并行块,用fork…end语句表示,并行块里的语句是同时执行的。

顺序块和并行块可以嵌套使用。

如果在begin或者fork语句后面加上名字,这个块语句就成了命名块,例如

begin :xiaomo

……

end

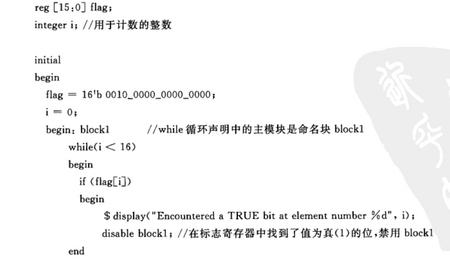

命名块有什么好处呢?有了命名块,我们就可以用verilog提供的disable语句来随时终止命名块,例如disable xiaomo;这样,当程序运行到此时,就会禁用命名块,就会直接跳出块语句,相当于C语言里面的break语句一样,看下面这个例子:

6、生成块

生成块语句可以动态的生成Verilog代码,这一声明语句方面了参数化模块的生成。党对矢量中的多个位进行重复操作时,或者进行多个模块的实力引用时,或者在根据参数的定义来确定程序中是否应该包括末端Verilog代码的时候,使用生成语句能够大大简化程序的编写过程。

生成语句可以控制变量的声明、任务或函数的调用,还能对实力引用进行全面的控制。编写代码时必须在模块中说明生成块的实例范围,关键字 generate…endgenerate用来指定该范围。

Verilog中有三种生成语句的方法,分别是循环生成,条件生成和case生成。

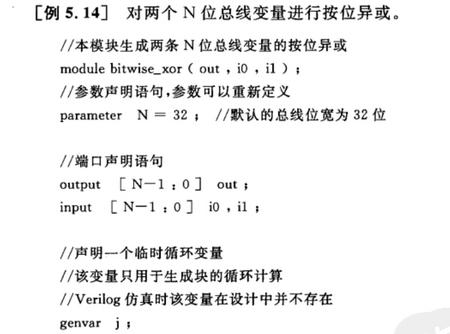

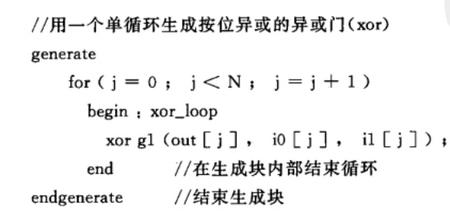

(1)循环生成

注:genvar 是关键词,用于生成生成变量,生成变量只存在于生成块中,在确立后的方针代码中,生成变量是不存在的。

xor_loop是赋予生成语句的名字,目的在于沟通它对循环生成语句之中的变量进行层次化引用。因此循环生成语句中的各个异或门的相对层次为:xor_loop[0].gl,xor_loop[1].gl…,xor_loop[31] 这句话什么意思啊

这个例子中的 xor gl (out [ j ] , i0 [ j ], i1 [ j ] );什么意思??求大神指点

当然这个异或门还可用always块实现

生成块程序

generate

for (j=0;j

begin :xiaomo

always @(i0[ j ] or i1[ j ]) out [ j ]=i0[ j ]^i1[ j ];

end

endgenerate

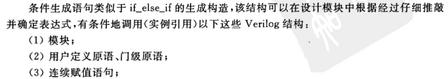

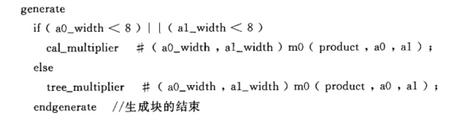

(2)条件生成

下面是一段生成语句

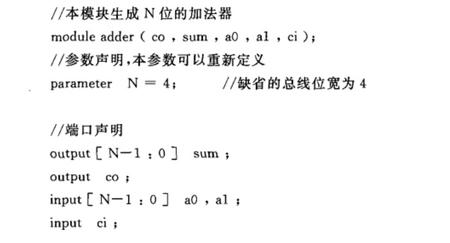

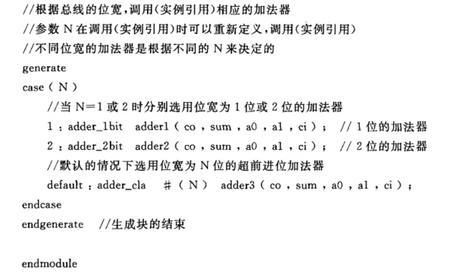

(3)case生成

下面是一个例子使用case语句生成N位的加法器

说实话上面这些东西我自己也是看的模模糊糊,好多地方不懂,只能先截个图放这儿了。唉...基础还是不行啊...

fpga相关文章:fpga是什么

c语言相关文章:c语言教程

评论