ARM存储器之:存储保护单元MPU

(3)c3中的MPU相关位

c3的编码格式如图15.20所示。

图15.20协处理器寄存器c3编码格式

寄存器位0~7分别对应域0~7的写缓存属性。位8~31应该设置成0。

当用指令MCR/MRC对c3进行读写时,第二个操作数opcode2>将被忽略,在指令要设置成0。

当配置数据域时,域的Cache位和写缓存区位一起决定域的访问策略。写缓存位有两个用途:使能/禁止域的写缓存和设置域的Cache写策略。域的Cache位控制写缓存位的作用。具体位分配见表15.16。

表15.16 Cache位和写缓存位的分配策略

Cache位 | 写缓存区位 | 域属性 |

C=0 | B=0 | 禁止Cache、禁止写缓存 |

C=0 | B=1 | 禁止Cache、使能写缓存 |

C=1 | B=0 | 使能Cache,域使用回写策略 |

C=10 | B=1 | 使能Cache,域使用直写策略 |

(4)访问权限寄存器c5

协处理器CP15的寄存器c5设置内存域的访问权限。

寄存器c5的编码格式如图15.21所示。

图15.21寄存器c5的编码格式

读寄存器c3的bits[15:0]存放域的AP(accesspermission,访问权限),其中bits[2n+1:2n]对于域n的访问权限。AP编码与访问权限的对应关系如表15.17所示。

表15.17 AP编码与访问权限的对应关系

AP编码 | 管理者 | 用户 |

00 | 不可访问 | 不可访问 |

01 | 读/写 | 不可访问 |

10 | 读/写 | 只读 |

11 | 读/写 | 读/写 |

对于Arm940T、Arm940T两个内核版本来说,使用MRC和MCR指令对其进行读写时,第二个协处理器寄存器CRm>将被忽略,指令中以c0的形式出现。对于指令数据统一的域,第二操作数opcode2>要设成0,而对于数据和指令分离的系统,如果opcode2=0,说明操作对数据域有效,如果opcode=1,说明操作对指令域有效。

| 注意 | 对于Arm946E-S和Arm1026EJ-S两个内核版本,它们的访问权限机制更复杂,采用的是扩展AP,扩展组AP位域编码支持两个增强的权限域,对其进行操作的MRC和MCR指令形式更复杂,有关更详细的内容,请参加Arm公司的用户手册。 |

(5)域大小控制寄存器c6

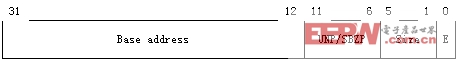

Arm系统中通过写协处理器c6来定义域的大小,通过MCR指令中第二个操作寄存器赋不同的值来指示是对哪个具体域进行操作。第二个操作寄存器取值为c0~c7,分别对应域0~域7。

每个域的起始地址必须对齐到其大小的整数倍。比如,一个域的大小位64KB,其起始地址可以是0x10000的整数倍的任何数。域的大小可以是4KB~4GB的2的任意乘幂。

寄存器c6的编码格式如图15.22所示。

图15.22域大小控制寄存器c6编码格式

存储器相关文章:存储器原理

评论