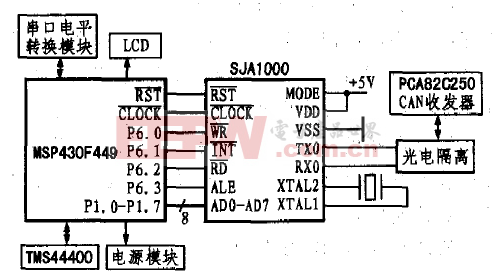

FPGA实现CAN总线通信节点设计

图4 接收数据流程图

2.2 FPGA 顶层模块设计

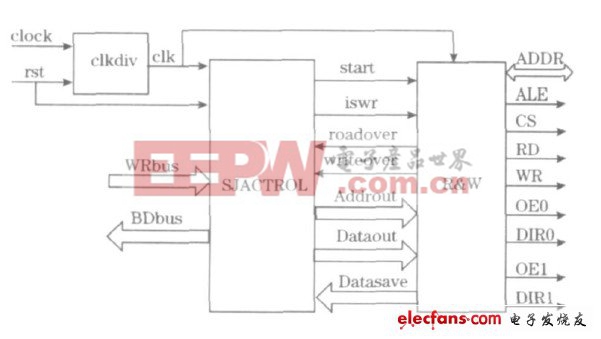

FPGA顶层的模块设计如图5 所示。其中c lkdiv 模块是将输入的50MH z时钟clock十分频后作为模块基准时钟。SJACTROL模块是控制总线通信的主模块, 而RW 模块则是根据主模块的信号生成SJA1000所需要的读写时序信号。SJACTROL模块通过start和isw r两个信号通知RW 模块是否要进行读或写总线操作。若是写操作, 则将地址和数据通过Addrout和Dataout传递给RW, RW 将负责把数据准确地送到S JA1000的数据地址复用总线ADDR, 并驱动SJA1000接收数据, 在写操作完成后发送w riteover信号通知SJACTROL写操作完成。读操作时RW根据SJACTOL送来的地址, 从SJA1000的数据总线上读取数据, 并将得到的数据通过Datasave 总线返回给SJACTROL。

图5 顶层模块设计

SJACTROL的状态机通过5个状态的转换来实现控制: 空闲状态、初始化状态、查询状态、读状态、写状态。RW 则是按照SJA1000的芯片数据手册进行时序逻辑设计。在编写模块时, 需注意双向总线的编写技巧。双向口最好在顶层定义, 否则模块综合的时候容易出错。

3仿真结果

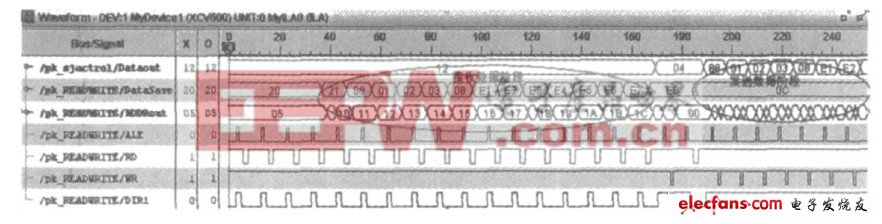

FPGA中利用Verilog 编程产生SJA1000的片选信号CS, 地址锁存信号ALE, 读写信号RD、WR.这些控制信号共同驱动SJA1000进行数据接收和发送。设计选取的是v irtex系列的芯片, 逻辑开发在ISE 平台上进行。在FPGA 的调试阶段, 使用xilinx的应用软件 ChipScope pro( 在线逻辑分析仪) 来在线观察FPGA设计内部信号的波形, 它比传统的逻辑分析仪更方便。图6为在线进行数据传送接收时的实际波形。

图6SJA1000接收和发送数据的时序仿真

4 结束语

实现了CAN 总线的通信功能, 系统工作状态良好。实践证明CAN 通信节点采用FPGA作为核心控制单元, 与传统的单片机设计相比, 更加灵活并且扩展性更强。

fpga相关文章:fpga是什么

通信相关文章:通信原理

晶振相关文章:晶振原理 双绞线传输器相关文章:双绞线传输器原理

评论