FPGA实现CAN总线通信节点设计

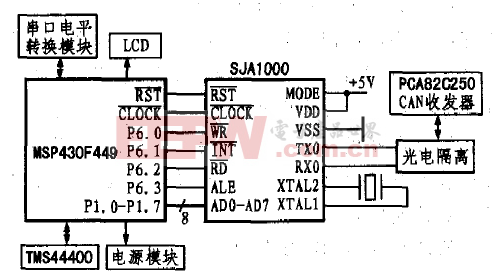

图2 接口电路

2 系统软件设计

2.1 设计流程

FPGA对CAN 总线通讯模块的控制主要包括3 部分: CAN总线节点初始化、报文发送和报文接收。由于通讯模块对接收数据的实时性要求并不是很高, 因此CAN 总线的数据接收和发送采用查询方式。

2.1.1 初始化过程

系统上电后首先对82C250 和S JA1000 进行初始化, 以确定工作主频、波特率、输出特性等。SJA1000的初始化只有在复位模式下才可以进行, 初始化主要包括工作方式的设置、验收滤波方式的设置、验收屏蔽寄存器( AMR )和验收代码寄存器( ACR)的设置、波特率参数设置和中断允许寄存器( IER) 的设置等。在完成SJA1000 的初始化设置以后, SJA1000 就可以回到工作状态, 进行正常的通信任务。设计中使SJA1000工作在PeliCan的方式下。

2.1.2 发送过程

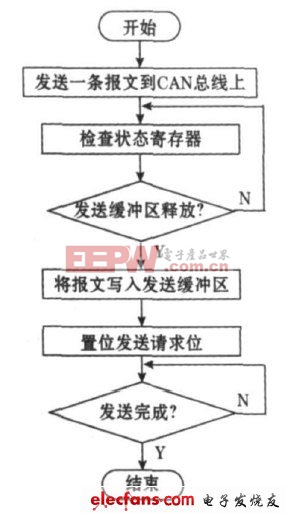

发送时, 用户只需将待发送的数据按特定的格式组合成一帧报文, 送入SJA1000发送缓冲区中, 然后启动SJA1000发送即可。当然, 在往SJA1000 发送缓存区送报文之前, 必须先判断发送缓冲区是否锁定, 如果锁定则等待; 判断上次发送是否完成, 未完成则等待发送完成。FPGA 通过SJA1000 向CAN 总线进行数据发送的流程图如图3所示。

图3 发送数据流程图

2.1.3 接收过程

接收子程序负责节点报文的接收以及其他情况处理。接收子程序比发送子程序要复杂一些, 因为在处理接收报文的过程中, 同时要对诸如总线关闭、错误报警、接收溢出等情况进行处理。只有在总线正常, 没有错误报警, 并且接收缓冲区中有新报文, 才开始进行数据接收操作。对接收缓冲区的数据读取完毕后释放CAN接收缓冲区。FPGA 通过SJA1000接收CAN总线上的数据流程图如图4所示。

fpga相关文章:fpga是什么

通信相关文章:通信原理

晶振相关文章:晶振原理 双绞线传输器相关文章:双绞线传输器原理

评论