基于Python 定点平方根的FPGA实现

FPGA 作为可编程的逻辑器件,它具有功耗低、便于修改、调试等特点,并能在上面实时完成大量的算法,平方根运算作为信号和图像处理中的常见算法,目前在FPGA上有许多实现,但是这些实现方法通常采用目前硬件设计中普遍采用的Verilog和VHDL语言进行硬件设计,这种设计方法存在着仿真和校验效率低,对于复杂的算法和软件设计者之间的沟通较为困难等问题。

本文引用地址:https://www.eepw.com.cn/article/226797.htmPython是一种简单易学并且功能强大的编程语言,并具有强大的软硬件描述能力,MyHDL采用Python扩展包的形式使其能支持硬件设计和仿真并在仿真结果符合要求后可将软件算法自动转换为相应的Verilog 或VHDL硬件描述。

本文试图采用这种新的基于Python的软硬件设计方法在FPGA上实现定点平方根。

1 方法

1.1 定点数表示

通常在FPGA 上的运算可以采用定点和浮点两种方式来实现,定点运算和浮点运算相比尽管数表示的范围较小,设计较为复杂,但是速度较快,占用FPGA资源较小,本设计采用定点来完成。平方根的输入为非负数,包括符号位为定点32位输入,其中高16位为整数部分,低15位为小数部分,可以直接计算的平方根范围为(65 536,0],结果采用32位输出,最高位为符号位,接着的高8位为整数部分,低23位为小数部分。

1.2 平方根实现

平方根的FPGA实现方法很多,有的算法为了减少片上资源的使用,逻辑实现上尽量避免使用乘法,比如CORDIC,逐位计算,non-restoring 等,现在FPGA上通常都有硬件乘法器,可采用迭代法和泰勒级数展开,本文采用泰勒级数展开的方法,级数采用5级,系数采用3.15的定点表示形式,小数部分15位,整数部分2位为了保证后续计算结果不溢出,整个位宽为18位,计算公式如式(1)所示:

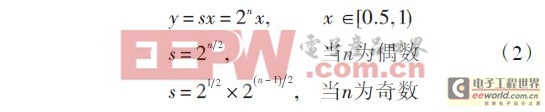

对于输入x 位于(65 536,0]之间,由于数的范围较大,通常进行归一化处理,采用的方法通过左移运算去掉二进制定点数的所有前导零,将输入的数转换为定点小数[0.5,1)之间,在完成平方根运算之后,然后根据前导零个数的奇、偶性不同分别进行去归一化处理,原理如式(2)所示,将输入数y 分为sx,s=2n,n 即为y 的二进制前导零的个数。

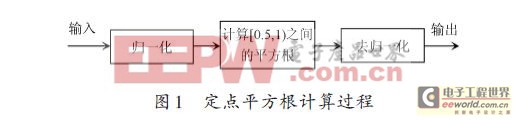

整个过程的设计模块如图1所示。

1.3 Python软硬件协同设计

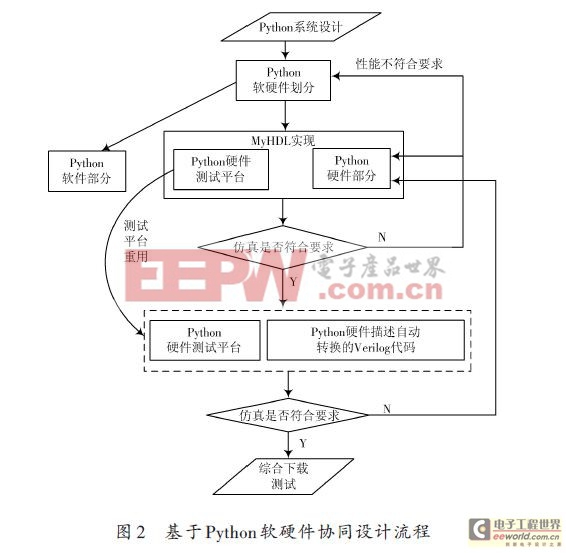

基于Python 的软硬件协同设计的过程如图2 所示,由于本设计最终要在硬件上实现,在设计时Python的硬件设计部分采用MyHDL 可综合子集,最后使用MyHDL的toVerilog()函数将MyHDL设计自动转换为相应的Verilog 代码,由于MyHDL 支持与Verilog 混合仿真,设计时的测试平台可以重用,仿真速度和设计效率大大提高。在完成基于Python软硬件设计并仿真正确之后,就可以回到进行传统的FPGA 设计流程,进行后续的下载,综合和测试工作。

2 结果

2.1 实验环境

采用MyHDL 0.8,采用GTKWAVE 查看仿真波形,FPGA 器件采用Altera公司CycloneⅡ 2C35F672C6,编译综合采用Quartus 12.1sp1 webpack.

2.2 仿真波形

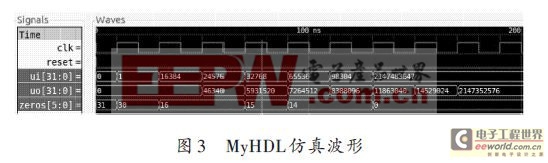

在设计过程中生成的VCD仿真波形可以随时采用GTKWAVE 查看,可以便于校验设计是否正确,最终完成的仿真波形如图3所示。

2.3 测试数据,精度及误差

由于整个过程采用Python设计,Python存在大量的软件包可以使

评论