基于Python 定点平方根的FPGA实现

2.4 综合结果

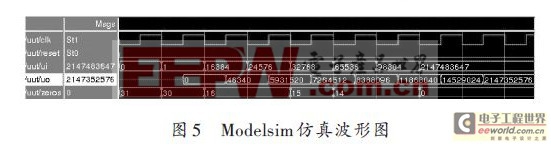

在上面仿真校验符合设计要求后,将Python自动转换为Verilog描述,采用Quartus编译综合,并使用Model-sim仿真的波形如图5所示,与图3的Python环境下仿真波形相似,由此可见采用Python的软硬件协同设计方法能有效地进行FPGA 设计。综合后FPGA 资源使用情况:LE共1 506个,寄存器64个,嵌入式9位硬件乘法器10个。

3 结论

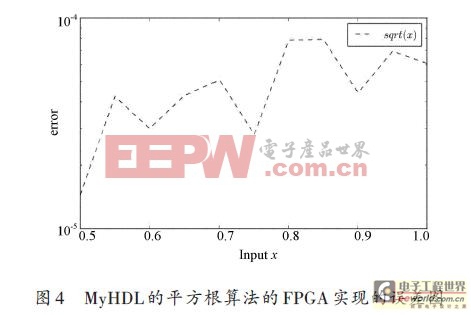

本文采用基于Python的扩展包MyHDL的软硬件协同设计方法,在FPGA 上完成了定点平方根算法,设计仿真过程仅使用Python语言,所以仿真校验和传统的设计方法相比效率更高,仿真速度也更快,另外此方法还可以方便,有效地将一个软件算法快速地转换为其相应的硬件实现,从而完成软硬件系统协同设计。

现代系统的算法越来越复杂,传统的软硬件设计方法越来越不适应市场对设计的要求,采用Python进行系统设计,仿真和校验的速度会大大地提高,也能够自动将算法转换为对应的硬件实现,所以采用Python来进行软硬件协同设计的产品能更快地进入市场,并且随着设计复杂性的进一步增强和这种设计方法本身的发展和完善,基于Python的软硬件协同设计方法将会有更加广阔的应用前景。

评论