一种出租车计价器的FPGA设计方案及应用

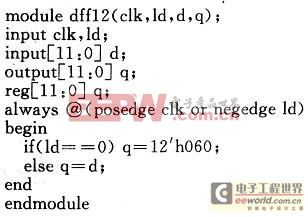

2.3 缓冲器模块

三位BCD码加法器输出的结果通过缓冲器以后,反馈到输入端重新作为一个加数,在1km脉冲信号的作用下,每来一个脉冲就和单价相加,形成连续累加的功能。缓冲器还有一个控制输入端LD,LD=O时,在1km脉冲的作用下,输出起步价6元;LD=1时,在1km脉冲的作用下,输出和输入相等。缓冲器的Verilog HDL源程序如下:

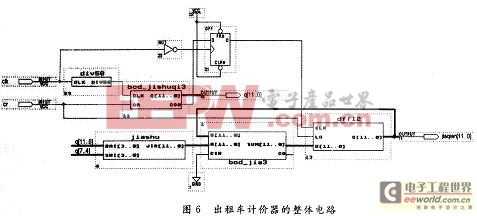

2.4 整体电路

将各个模块按照输入输出关系连接成整体电路如图6所示。

在整体电路中,clk为最原始的时钟输入端,cr为异步清零端,q[11..O]输出里程,jiaqian[11..O]输出乘客应付的费用。

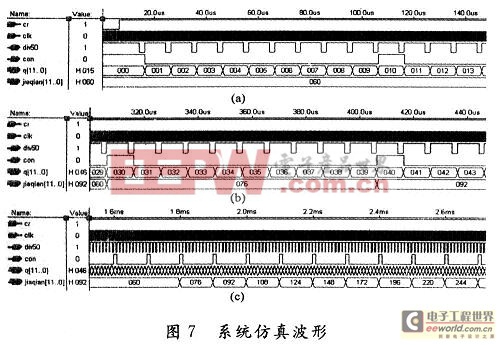

3 系统仿真验证

整体电路的仿真波形如图7所示。

从系统仿真波形图7(a)中可以看出,当清零端cr=O时,里程数立刻清零,乘客应付的费用显示三位十进制数060(起步价6元),表示乘客刚上车。当清零端cr=1时,出租车开始行进,里程和费用都开始计数,里程显示三位十进制数,前两位为整数,第三位为小数,也就是每行驶100 m计一次数。

从系统仿真波形图7(b)中可以看出,行驶到3 km时,费用由6元增加为7.6元,行驶到4 km时,费用由7.6元增加为9.2元,在3~7 km之间时,每行驶1 km增加1.6元。

系统仿真波形图7(c)中显示了每行驶1 km后,费用逐渐累加的情况。系统仿真波形完全验证了预期的设计要求。

4 结 语

通过仿真验证表明,本文所设计的出租车计价器能够正常地显示行驶的里程数和乘客应付的费用,符合预定的计费标准和功能要求。基于FPGA的设计,集成度高、设计周期短。尤其是当计费标准发生变化时,容易通过改写Verilog HDL源程序来完成新的设计。

评论