基于FPGA和VHDL的USB2.0控制器设计

2 控制器实现

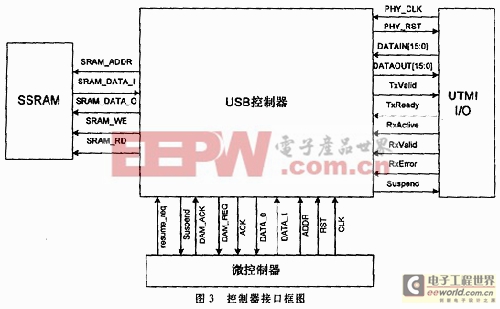

控制器接口的信号框图如图3所示。存储器采用标准的单口SRAM,其信号接口由32位数据线SRAM_DATA、15位地址线SRAM_ADDR及读写信号(SRAM_WE和SRAM_RD)组成,系统所需SRAM的容量为2 15×32bit=128KB。

而与微控制器之间的接口信号包括32位数据线DATA、18位地址线ADDR以及DMA请求和响应信号(DMA_REQ和DMA_ACK)。由于要支持到128KB,需要17位地址线,另外还需要一根地址线来选通SSRAM和USB控制器内部的寄存器,总共需要18根地址线addr[17:0]。定义如下:

USB_RF_SEL = !addr[17];

USB_MEM_SEL =addr[17];

第18位地址addr[17]为高时选择缓冲存储器,否则选择内部寄存器。地址addr[16:2]直接用于存储器SSRAM的地址。

2.1 UTMI接口

UTMI接口信号包括:与发送数据相关的信号(TxValid、TxReady等),与接收数据相关的信号(RxActive、RxValid、RxError等)以及16位双向数据线。

在物理层,该控制器需要一个外部的USB收发器(Transceiver),本文采用的是Philips公司的ISP1501芯片。该芯片用作USB2.0的模拟前端,从USB电缆来的差分信号进行反转不归零码(NRZI)解码和位解填充转换成16位并行数据;反之,16位并行数据通过一个差分驱动电路经过串行化、位填充和NRZI编码输出到USB电缆上。ISP1501通过管脚MODE0和MODE1决定收发器的工作模式,共有4种工作模式:MODE[1:0]为“00”时,收发器处于断开状态;为“01”时处于全速(Full Speed)模式(此时USB带宽为12Mb/s);为“10”时是高速(High Speed)模式(此时USB最大带宽是480Mb/s);为“11”时是HS chirp模式。

UTMI接口通过译码MODE[1:0]来控制ISP1501在HS和FS之间转变。

If mode_hs='1'then

MODE='10'

Elsif mode_hs='0'then

MODE='01'

End if;

评论