一种基于FPGA的高速通信系统研究与设计

2 系统的硬件设计

2.1 FPGA部分电路设计

系统选用Xilinx公司Spartan3系列的FPGA:S3C500E。它有10 476个逻辑单元,232个I/O,4个时钟管理模块(DCM),存储器包括360 Kb的块RAM和73 Kb的离散RAM。所有I/O可以组成92组LVDS差分对,最高输入输出速率高到622 Mb/s,所以系统不需要额外的电路实现LVDS接口。DCM模块可以将输入时钟灵活的倍频或降频,最高工作频率达到311 MHz。以上参数和性能不仅满足当前的设计需求,而且为系统的升级保留了充足的设计余量。FPGA外围电路包括时钟部分和配置部分。时钟使用电路板上的晶振提供,通过GCLK脚与FPGA相连。GCLK是专用时钟引脚,这个脚的驱动能力强,到所有逻辑单元的延时基本相同。配置电路采用主动SPI模式。相比其他模式,主动SPI模式的外围电路简单、体积小、成本低。而且SPI FLASH的容量大,除了存储配置文件,还可以存储其他用户数据。S3C500E的配置文件大小为2 Mb,本系统采用存储量为16 Mb的M25P16作为配置存储器。

2.2 传输部分电路设计

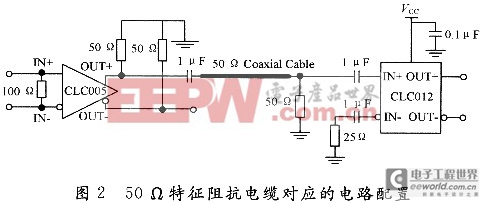

传输部分设计包括选择同轴电缆和设计相应的发送接收电路。本系统选用的同轴电缆型号为SVY-50-3,成本低、性能好。这款电缆的特征阻抗为50 Ω,速率150 MHz时信号传输100 m的最大衰减为18.01 dB。它具有良好的屏蔽特性,可以在复杂的电磁环境中正常工作。电缆驱动电路和接收均衡电路分别选用National Semiconductor公司的芯片CLC005和CLC012。CLC005支持LVDS电平输入,最高传输速率达到622 Mb/s,输出信号峰一峰值从O.7~2 V。CLC012可以自动均衡频率在50~650 MHz的信号。时钟恢复器件选用CLC016,它的输入信号来自CLC-012,输出时钟和数据接FPGA,恢复的时钟在数据上升沿有效。CLC005和CLC012用于特征阻抗为75 Ω的传输系统,针对本系50 Ω特征阻抗的同轴电缆,需要改动外围电阻配置,否则会因为阻抗不匹配引起信号反射,最终导致信号传输质量下降。相应的配置方式如图2所示。

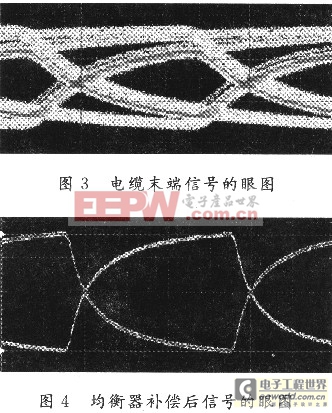

通过测试,此组传输器件可以驱动LVDS信号通过SVY-50-3型号电缆传输至少200 m。信号经过传输后,在电缆末端衰减严重,噪声和抖动也较严重。此时信号眼图如图3所示,可以看出信号质量差。直接接收此信号,会产生信号电平误判,而且信号的抖动将导致后级电路无法正常工作。接收均衡器CLC012自动为信号损耗提供补偿后,信号上的噪声和抖动均得到了改善,信号的眼图如图4所示。

评论