基于FPGA的数据中继器设计

4 测试与分析

高速数据中继器设计制板完成后,还要将其置于整个路由器环境中进行性能测试,其测试结构如图三所示,最下面四个模块组成了高速数据中继器。

图 三:测试结构图

从图中可以看出,测试时需要两个10GbE接口,一个用于接收测试仪的数据报文,另外一个则是对经过转发处理和端口交换后的数据报进行处理后返回给测试仪进行分析。下面给出衡量系统性能的关键参数的测试情况。

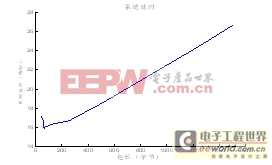

测试中选用的数据包长是46、60、64、65、128、256、512、1024、1280、1508,测试时间是1分钟,测试结果如下:

图 四:系统时延测试曲线图

由于我们的中继器设计时的性能指标是可以达到10Gbps速率下40字节IP包的处理能力,在测试仪的吞吐量下不应该丢包,实际测试结构在上述10种包长的情况下,IPv4和IPv6的单播、组播包的丢包率均为0。系统时延测试结果如图四所示。从测试结果可以看出,高速数据中继器应用在高速路由器中后完全满足高速路由器对数据中继要求的各项性能指标。

5 创新点总结

本文的创新点是提出了一种基于FPGA的高速数据中继器设计方案,并综合分析了ASIC和NP等方法设计的高速网络中继器设计方法,在设计的功能和灵活性两方面做了很好的权衡。从测试结果可以看出,本文设计很好地满足了网络处理的基本功能以及高速数据中继的性能指标要求。

评论