基于FPGA的数据中继器设计

3 方案的选取与实现

从以上输入处理和输出处理流程来看,物理层和链路层的功能可以通过选择相应的商用器件来实现,实现起来并不复杂;但图1中虚线框内的处理功能是在10Gbps的高速率下进行的,实现起来比较困难。目前在高速数据处理中,能完成这部分功能的处理器件可分为固定功能器件和可编程器件两种,其中固定功能器件主要指ASIC(Application Specific Integrated Circuit),可编程器件又有FPGA(Field Programmable Gate Array)和NP(Network Processor)两种,下面对这三种器件进行比较。

首先能够同时提供极高转发性能和较低成本的只有ASIC芯片了。ASIC的硬件资源最为丰富,处理能力是NP不能比拟,万兆核心层设备采用ASIC是对于性能的一种保障。但是它的先天不足也是无法回避的,由于ASIC的固定特性一直无法解决路由器对多业务支持的需求,ASIC芯片一旦产出后,其原有的功能无法添加,也可以把业内目前需要的功能都做在ASIC里面,但是现在主流的很多技术如MPLS、QoS等都是只停留在草案阶段,还未标准化,所以现在就做死在ASIC里面显然是有很大风险的。由此可看出,ASIC可为任何固定功能提供高性能,但却几乎没有灵活性和可扩展性。第二种NP,目前网络处理器(NP)技术是业内非常受欢迎的技术之一,NP技术本身就是通过厂家自己编写微码的方式对网络协议处理进行优化,通过内置微引擎的方式实现加速处理,性能是CPU无法比拟的。这样的结构注定了NP就比ASIC拥有更多的灵活性,对新增业务的支持能力永远都比ASIC强。但是NP也有其自身不能克服的缺点,NP的硬件资源对比ASIC肯定还是有很大差距的,所以其在处理海量多业务时转发性能下降很快,不能达到线速。

第三种是FPGA,FPGA对任何高速并行数据处理都非常理想,具有可编程的能力和较高的灵活性,便于实现多业务支持,同时,由于其可编程性是通过硬件实现的,因此可以提供较高的高速数据处理性能。考虑到硬件的可编程性没有软件灵活,所以最新的FPGA上可以加上一个微处理器的核心(core),加上了微处理器核心的FPGA,在可编程性上变得“软硬兼备”。 除了加上微处理器的核心,FPGA芯片公司还花大力开发芯片的高速I/O,通过网络友好的功能,该类型FPGA可提供高性能数据和网络控制处理功能。这使他们成为WAN/MAN/LAN网络中专用高速数据处理的理想候选器件,并将在灵活性/性能间进行折衷的控制权交到用户手中。此外,FPGA对任何高速数据的并行处理都比较理想,而且具有非常的灵活性和扩展性,且开发周期短,能够形成具有自主知识产权的内核,最终还可以形成自己的ASIC,因此在本文设计中选择了FPGA作为高速数据处理的核心部件。

根据高速数据中继器的功能需求,并考虑高速数据中继与转发中路由器的实际性能指标,确定了该高速数据中继器需要达到以下技术指标:具有10Gbit/s线速度处理40字节长IP包的能力;支持100MSPS的查表速度;可提供64K条本机地址表项。

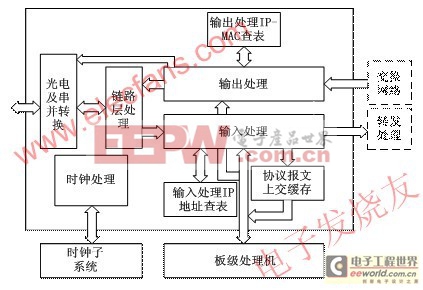

从上述三点性能指标来看,第一点通过选择性能指标高的FPGA即可实现,而第二点和第三点则无法由FPGA单独完成。从这两点性能指标来看,都是关于路由查表方面的,一个是表项容量方面的指标,一个是查表速度方面的指标。目前流行的查表方案是采用CAM(Content Addressable Memory)来实现,因此本文总体设计中也采用CAM来实现查表处理。由此得出的高速数据中继器总体设计结构如图二所示。

图 二:基于FPGA的数据中继器设计结构

在该设计结构中,输入处理和输出处理使用FPGA来实现,由于这些处理功能都是在10Gbps的高速下完成的,占用的FPGA资源较多,加之输入输出处理时都有查表模块,占用的FPGA I/O资源也较多,要在一片FPGA内完成这些处理功能是很困难的。为降低设计难度和为以后功能扩展预留一些FPGA资源,对输入处理采用一片FPGA来完成,对输出处理同样采用一片FPGA来完成。对于其他功能部分,控制管理平面(板极处理机)采用Power PC来实现,输入查表和输出查表使用CAM来实现。在10G以太网链路层处理上选用商用ASIC芯片S19205来实现,S19205可以兼容IEEE802.3ae标准,能工作在10G-LAN、10G-WAN和10G-POS(Packet Over SDH)三种模式;在10G以太网的PMA和PMD子层的功能实现上选用了Gtran公司的GT10来实现,它是一个Transponder,在内部即实现了光电转换,又实现了串并转换,通过提供不同的时钟网络配合S19205就可以实现这三种10G接入方式。对于10G-LAN接入和10G-WAN接入而言,FPGA程序的处理流程是相同的,这样,S19205在GT10的配合下,可以将10G-LAN和10G-WAN的差别屏蔽在FPGA功能处理之外,使得该设计结构既可工作在10G-LAN模式,也可工作在10G-WAN模式,达到设计复用的目的。

评论