基于单片机的EPS驱动电路设计

2.3.1 H桥上侧桥臂MOSFET功率管驱动电路设计

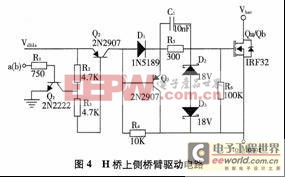

上侧桥臂的MOSFET功率管驱动电路如图4所示,其中Qa/Qb为上侧桥臂的功率MOSFET a管或b管,vdble为倍压电源电路提供的电源电压。当MOSFET的控制信号a(b)为高电平时,Q1和Q2导通,电源通过Q2,D1以及R5与C1的并联电路向Qa充电,直至Qa完全导通,Q3截止。当Qa导通时,忽略Qa的漏极和源极之间的电压降,则Qa的源极电压等于蓄电池电源电压。此时,Qa的栅-源极电压降VGS=( Vdble-VCE-VF-Vbat),其中VCE为2N2907的集一射极饱和导通电压,其典型值为0.4V,VF为D1的正向导通压降,其典型值为0.34V,Vbat为蓄电池电压。为保证器件可靠导通,降低器件的直流导通损耗,VGS不低于l0V。因此需设计高效的倍压电源电路,以保证Vdble的值足够大,满足功率MOSFET的驱动要求。如果蓄电池电压为12V时,Vdble≥12V+0.34V+0.4V+10V=22.74V。

当MOSFET的控制信号a(b)管为低电平时,Q1和Q2均截止,Q3导通,Qa的栅-源极电压通过R5与C1的并联电路及Q3迅速释放,直至Qa关断。Qa关断时,连接其栅-源之间的电阻R6使其栅-源电压为零。IRF3205的导通门限电压为2~4V,OV的栅-源极电压能够使其关断。

2.3.2 下侧桥臂的功率MOSFET管驱动电路

下侧桥臂的功率MOSFET驱动电路如图5所示,其中Qc/Qd为下侧桥臂的功率MOSFET的c管或d管。当MOSFET的控制信号c(d)为高电平时,Q1导通,Q2截止,Q1的栅极电压通过R3与C1组成的并联电路、D1及Q1迅速释放,Qc/Qd关断。

评论