AD9856工作原理及在雷达回波模拟器中的应用

1 引言

本文引用地址:https://www.eepw.com.cn/article/20904.htm雷达回波模拟在雷达系统的设计、改进和定型中具有十分重要的意义。ad9856是美国adi生产的正交数字上变频器,其内部集成了1个高速直接数字频率合成器(dds)、1个12位高速、高性能数/模转换器、时钟倍频电路、数字滤波器及其他数字信号处理功能模块。它具有低成本、低功耗、体积小、动态范围大等优点,可以处理来自dsp的成型后的基带抽样值序列,将其上变频变为中频,产生雷达回波的中频模拟信号。ad9856可以应用在通信和雷达等系统中。

2 ad9856的工作原理

2.1 ad9856的基本功能

ad9856的基本特性和技术指标如下:

+3v单电源供电; 直流到80mhz的输出带宽;

在40mhz输出频率下具有大于52db的sf-dr,在70mhz输出频率下,sfdr大于48db,在70mhz输出频率下的窄带sfdr大于80db;

有采样率可编程的内插滤波器;

有可编程的参考时钟倍频器;

有内置的sinx/x补偿滤波器;

有双向控制总线接口;

支持突发和持续tx二种模式;

单频模式可用于直接频率合成。

2.2 ad9856的原理及各部分的功能

(1)数据复合和串并转换

ad9856的结构如图1所示。ad9856内部的数据格式是12bit的二进制补码。基带信号的i、q2路数据是交替输入的,数据复合器需对输人数据进行识别,将其转换成i、q2路并行数据流,送往下一级电路。

(2)半带滤波器(hbf)

半带滤波器(hbf)分为3级:hbfl、hbf2和hbf3。其中hbfi是47阶滤波器,hbf2是15阶滤波器,前2级hbf的联合内插损失仅为0.01db,hbf3是可选11阶滤波器,它对信号的损耗为0.03db。每级hbf可使数据的采样率提高1倍,为了使信号频带处于滤波器通带的平坦部分,需要提高hbf的截止频率,也就是说在数据输入ad9856之前要进行过采样。

(3)级联积分梳状滤波器

ad9856的cic实际上是可编程的过采样滤波器,过采样率的范围是2≤r≤63。随着r的改变, cic会引入不同的插入损耗。为了弥补这种损耗。用户可以设置cic增益位,使得cic的输出增大1倍。但在这种工作模式下,必须确保输出信号不会溢出。

(4)正交调制

ad9856的正交调制就是将基带信号的频谱移到所需要的载波频率上,即通常所说的上变频。正交调制所需要的余弦和正弦2路数字载波由1个高速直接数字信号合成器(dds)产生,其频率可以通过设置相应的寄存器来控制。这2路数字载波分别与cic输出的i、q数据相乘,然后再进行相加或相减,即得到调制后的数字中频信号。cic输出的i、q数据的采样率与dds数字载波的采样率是相同的,也就是ad9856的系统时钟采样率(sysclk)。所以,调制后的信号实际上是一组采样率为sysclk的数据流。

(5)数/模转换

调制后的数字信号要经过12位的dac转换成模拟信号。dac通过零阶保持实现数/模转换。由于存在零阶保持效应,所以其输出信号的频谱实际上是被sinc包络加权过的。因此需要在dac前面加上1个反sinc型滤波器(isf)对输人数据流进行处理,以校正sinc包络造成的失真。而数/模转换会在n*sysclk±fcarrier(n=1,2,3)处产生干扰信号,这些干扰信号可以通过1个外接rlc滤波器滤除。一般情况下,使用1个7阶椭圆低通滤波器即可。

ad9856提供2路互补的2个电流输出,输出电流的满额值iout范围是5ma~20ma,可以通过其25引脚的dac rset,来设置。其关系为 rset=39.936/iout

(6)控制单元

ad9856提供了1个灵活的同步串行通信接口,这个接口可以读写,ad9856的所有寄存器。控制单元根据各个寄存器的内容设置ad9856的工作模式。ad9856还提供了1个与ad8320(可编程电缆驱动放大器)串行通信的接口。控制单元可以通过这个串口直接设置ad8320的增益。

(7)输人数据模式

ad9856提供了二种输人数据的时序模式:突发模式和连续模式。在突发模式下.ad9856通过txenable的上升沿来保持与输人数据的同步。突发模式支持全部3种字长(12bit、6bit和3bit)。对于连续模式,txenable可以看成输入数据时钟。该信号除了用来同步外,还可以指示输入数据是i路还是q路(1表示i路,o表示q路)。连续模式只支持12bit字长。图2和图3分别示出二种输入模式的时序关系,其中internal i和internal q为数据分离所产生的并行i和q数据流。

3 在pd雷达回波模拟器中的应用

3.1 硬件组成

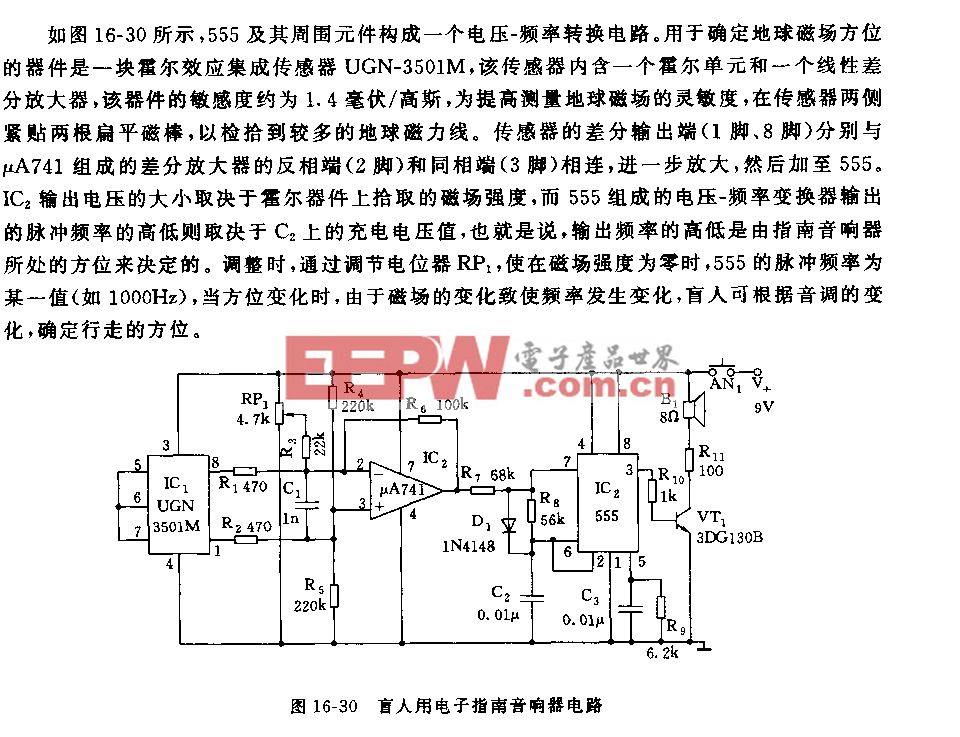

本系统由adi的qdu ad9856、dga ad8369、tsl01型dsp及altera公司的ep1k30型fpga组成,结构框图如图4所示。

在图4中,ts101产生正交i和q2路雷达回波数据,tsl0l通过外部总线将ad9856和ad8369的配置信息写入ep1k30。由于ad9856要求的配置信息是串行写入的,因此,需在ep1k30内将ts101送出的并行指令变为串行指令,并按照ad9856时序要求送入ad9856。将ad9856配置好后,tsl01以dma方式将正交i和q2路雷达回波数据通过数据总线送至ad9856,ad8369将ad9856产生的中频模拟信号放大后,送人下一级电路处理。

3.2 ad9856串口操作

同步串口包括cs、sync i/o、sclk、sdio和sdo 5条信号线。其中,cs为低有效串口使能信号;sync i/o为串口同步恢复信号,当串口失去同步后,可在sync i/o上加1个正脉冲使串口恢复初始状态;sclk为串口的数据时钟信号;sdio为双向数据线,当串口置于双线(sclk和sdio)方式时,sdio为双向数据线。当置于3线(sclk、sdio和sdo)模式时.其输出功能由sdo替代。对串口的操作有严格的时序要求,1个串口通信周期为指令周期和数据读写周期。在初始状态,串口等候sclk(上的8个上升沿指示的8bit指令,然后进行由指令设定的1-4个字节的数据读写,读串口由sclk下降沿指示,而写串口由sclk上升沿指示。完成后又等待下1个周期的到来。

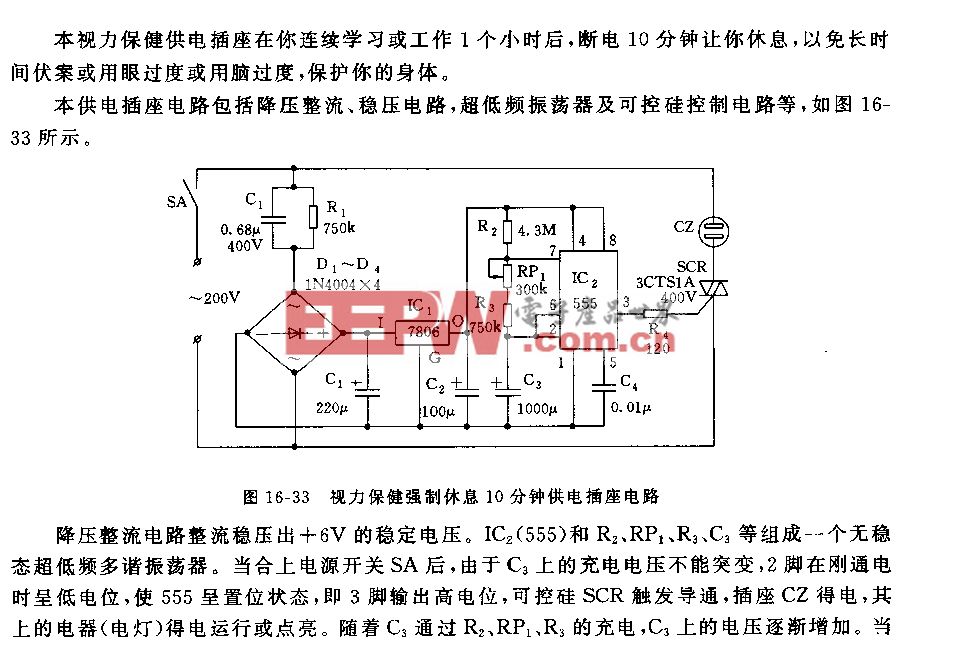

根据串口写时序要求设计控制电路,在fpga中实现ad9856的串口操作,对ad8369的控制也在此电路中实现。控制电路的原理框图如图5所示。

利用fpga将dsp输出的并行指令变换为串行,指令的转换时必须注意以下几点:

(1)串口支持msb在前和lsb在前二种格式,通过寄存器o的第6位设置,并且对该位的设置是立即有效的。即如果当前操作对该位进行修改,则下1个字节的传输就会采用新的格式。

(2)对多字节传输的通信周期,如果msb在前,寄存器地址递减;如果lsb在前,寄存器地址递增。

(3)外部控制器必须与ad9856同步,如果失去同步。可由sync i/o重新产生同步,不必对这个电路进行复位。

通过ad9856的串口设置好工作参数后,ts101以dma方式将正交的i和q2路数据交替送入ad9856得到正交上变频后的模拟信号。

4 结束语

本系统利用ad9856实现正交上变频,模拟了雷达回波波形,达到了预期的技术指标,在实际工程中运行良好。此外,此系统还可以产生通信中常用的2ask、2fsk和2psk等信号,试验证明其效果良好。

低通滤波器相关文章:低通滤波器原理

数字滤波器相关文章:数字滤波器原理

评论