3D集成电路如何实现

TSV也可以在CMOS器件制造完成之后制作。在键合工艺之前完成,或者在键合工艺之后完成。由于CMOS器件已经制作完成,因此在通孔形成时晶圆不需要再经受高温处理,所以可以使用铜导电材料。很明显,制作这些通孔的空白区域需要在设计芯片时就予以考虑。

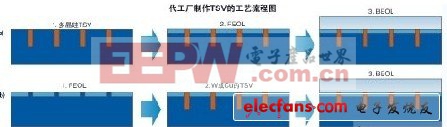

如果可以选择,无论是FEOL还是BEOL方案,只要是在晶圆代工厂制作TSV,都是相对简单的选择。BEOL互连层是一个拥有不同介质和金属层的复杂混合体。刻蚀穿透这些层很困难,而且是由不同产品具体决定的。在完整的IC制造之后通过刻蚀穿透BEOL层来制作TSV会阻碍布线通道,增加布线复杂性并增加芯片尺寸,可能会需要一个额外的布线层。既然诸如TSMC(中国台湾省台北)和特许(新加坡)等晶圆厂已宣称他们有意向量产化TSV制造,那么在IC制造工艺中制作通孔将成为一个更切实可行的选择。

评论